Max9489 multiple-output network clock generator, Table 2. register address mapping, Table 3. output frequency control – Rainbow Electronics MAX9489 User Manual

Page 10: Table 4. output frequency margin control

MAX9489

Multiple-Output Network Clock Generator

10

______________________________________________________________________________________

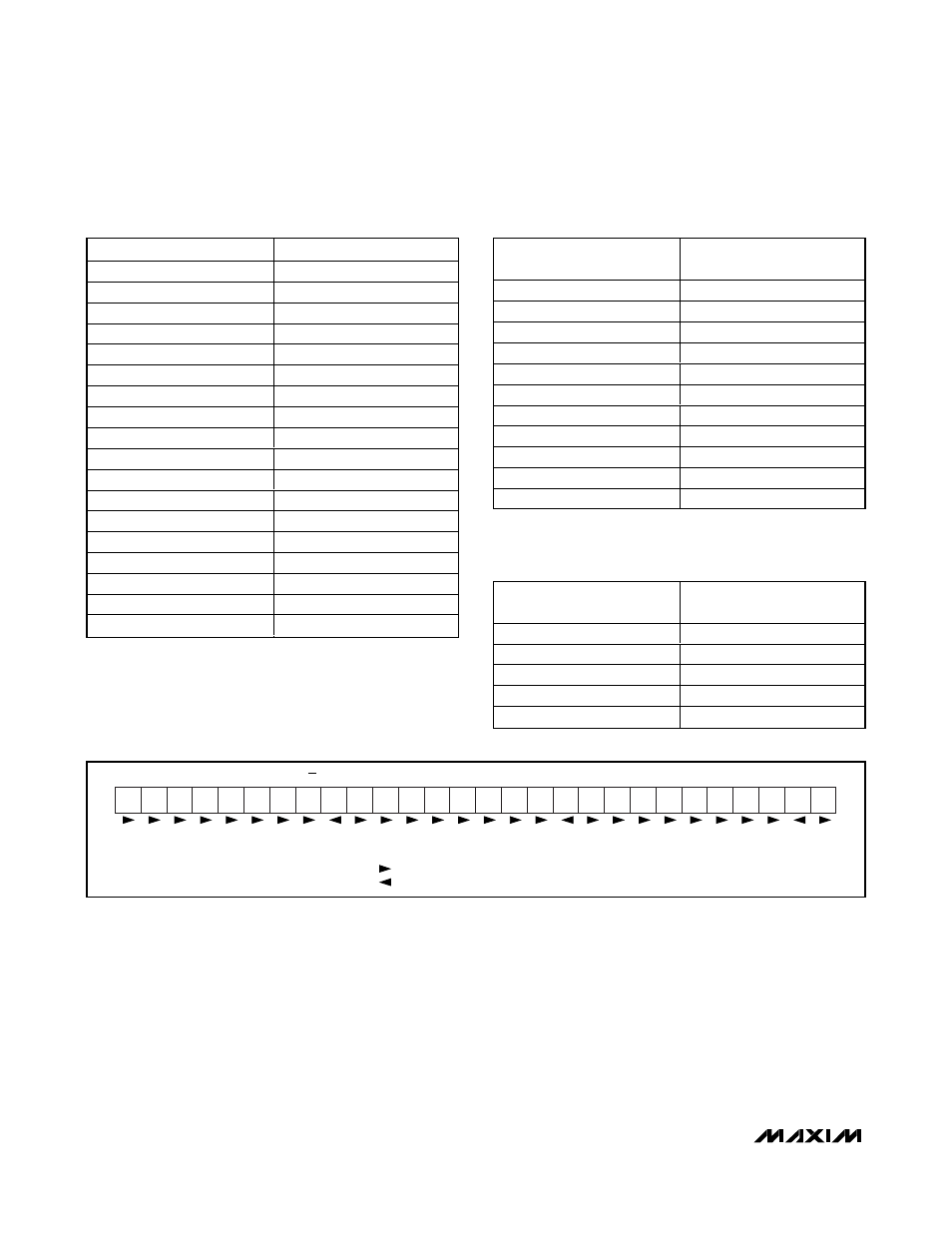

REGISTER ADDRESS BYTE

REGISTER FUNCTION

0x00

Broadcast to all CLK registers

0x01

CLK1

0x02

CLK2

0x03

CLK3

0x04

CLK4

0x05

CLK5

0x06

CLK6

0x07

CLK7

0x08

CLK8

0x09

CLK9

0x0A

CLK10

0x0B

CLK11

0x0C

CLK12

0x0D

CLK13

0x0E

CLK14

0x0F

CLK15

0x10

Frequency margin control

0x11 – 0xFF

Reserved, do not use

Table 2. Register Address Mapping

CLK_ REGISTER DATA

BYTE

OUTPUT FREQUENCY

(MHz)

0x00

Logic low*

0x01

133.3

0x02

125

0x03

100

0x04

83.3

0x05

80

0x06

66.6

0x07

62.5

0x08

50

0x09

33

0x0A

25

Table 3. Output Frequency Control

MARGIN REGISTER DATA

BYTE

OUTPUT FREQUENCY

(MHz)

0x00

0%

0x01

5%

0x02

10%

0x07

-5%

0x06

-10%

Table 4. Output Frequency Margin Control

*Power-up default for CLK2 through CLK15.

S

1

1

A4

A3

A2

A1

0

ACK

0

0

0

0

0

0

1

1

ACK

0

0

0

0

0

1

0

1

ACK

P

START

DEVICE ADDRESS

REGISTER ADDRESS

DATA IN

STOP

R/W

S = START CONDITION

A_ = DEVICE ADDRESS

ACK = ACKNOWLEDGE

P = STOP CONDITION

DATA DIRECTION

= MASTER TO SLAVE

= SLAVE TO MASTER

Figure 5. Example—Setting CLK3 to 80MHz