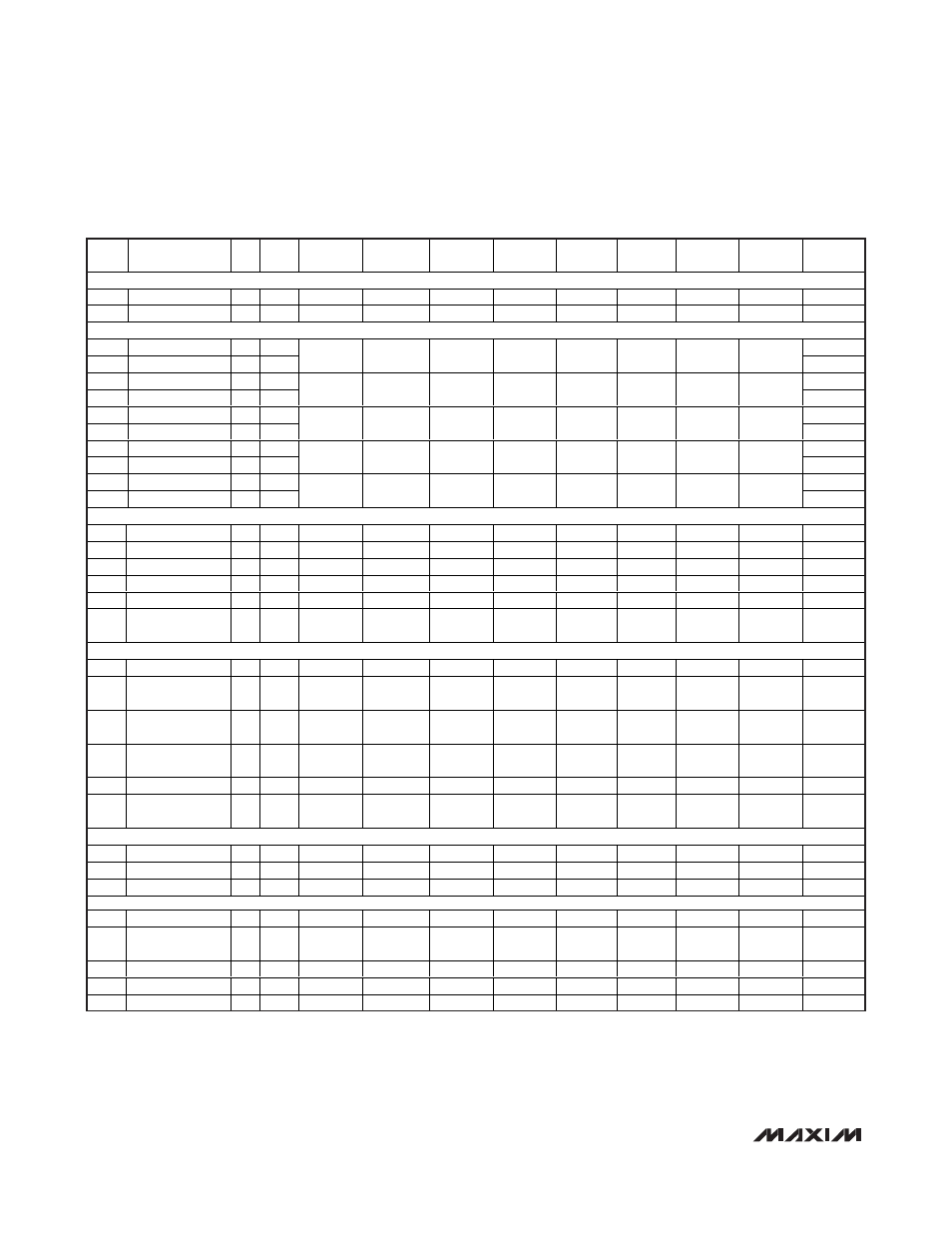

Table 37. register summary – Rainbow Electronics MAX5965B User Manual

Page 44

MAX5965A/MAX5965B

High-Power, Quad, Monolithic, PSE Controllers

for Power over Ethernet

44

______________________________________________________________________________________

ADDR

REGISTER NAME

R/W

PORT

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

RESET

STATE

INTERRUPTS

00h

Interrupt

RO

G

SUP_FLT

TSTR_FLT

IMAX_FLT

CL_END

DET_END

LD_DISC

PG_INT

PE_INT

0000,0000

01h

Interrupt Mask

R/W

G

MASK7

MASK6

MASK5

MASK4

MASK3

MASK2

MASK1

MASK0

AAA0,0A00

EVENTS

02h

Power Event

RO

4321

0000,0000

03h

Power Event CoR

CoR

—

PG_CHG4

PG_CHG3

PG_CHG2

PG_CHG1

PWEN_

CHG4

PWEN_

CHG3

PWEN_

CHG2

PWEN_

CHG1

—

04h

Detect Event

RO

4321

0000,0000

05h

Detect Event CoR

CoR

—

CL_END4

CL_END3

CL_END2

CL_END1

DET_END4

DET_END3

DET_END2

DET_END1

—

06h

Fault Event

RO

4321

0000,0000

07h

Fault Event CoR

CoR

—

LD_DISC4

LD_DISC3

LD_DISC2

LD_DISC1

IMAX_FLT4

IMAX_FLT3

IMAX_FLT2

IMAX_FLT1

—

08h

Startup Event

RO

4321

0000,0000

09h

Startup Event CoR

CoR

—

IVC4

IVC3

IVC2

IVC1

STRT_FLT4

STRT_FLT3

STRT_FLT2

STRT_FLT1

—

0Ah

Supply Event

RO

4321

0001,0000*

0Bh

Supply Event CoR

CoR

—

TSD

V

DD_OV

V

DD_UV

V

EE_UVLO

V

EE_OV

V

EE_UV

OSC_FAIL

V

DD_UVLO

—

STATUS

0Ch

Port 1 Status

RO

1

Reserved

CLASS1[2]

CLASS1[1]

CLASS1[0]

Reserved

D ET_S T1[ 2] DET_ST1[1]

DET_ST1[0]

0000,0000

0Dh

Port 2 Status

RO

2

Reserved

CLASS2[2]

CLASS2[1]

CLASS2[0]

Reserved

D ET_S T2[ 2] DET_ST2[1]

DET_ST2[0]

0000,0000

0Eh

Port 3 Status

RO

3

Reserved

CLASS3[2]

CLASS3[1]

CLASS3[0]

Reserved

D ET_S T3[ 2] DET_ST3[1]

DET_ST3[0]

0000,0000

0Fh

Port 4 Status

RO

4

Reserved

CLASS4[2]

CLASS4[1]

CLASS4[0]

Reserved

D ET_S T4[ 2] DET_ST4[1]

DET_ST4[0]

0000,0000

10h

Power Status

RO

4321

PGOOD4

PGOOD3

PGOOD2

PGOOD1

PWR_EN4

PWR_EN3

PWR_EN2

PWR_EN1

0000,0000

11h

Address Input Status

RO

G

Reserved

Reserved

A3

A2

A1

A0

MIDSPAN

AUTO

00A3A2,

A1A0MA

CONFIGURATION

12h

Operating Mode

R/W

4321

P4_M1

P4_M0

P3_M1

P3_M0

P2_M1

P2_M0

P1_M1

P1_M0

AAAA,AAAA

13h

Load Disconnect

Detection Enable

R/W

4321

ACD_EN4

ACD_EN3

ACD_EN2

ACD_EN1

DCD_EN4

DCD_EN3

DCD_EN2

DCD_EN1

0000,AAAA

14h

Detection and

Classification Enable

R/W

4321

CLASS_EN4

CLASS_EN3

CLASS_EN2

CLASS_EN1

DET_EN4

DET_EN3

DET_EN2

DET_EN1

AAAA,AAAA

15h

Backoff and High-

Power Enable

R/W

4321

EN_HP_ALL

EN_HP_CL6

EN_HP_CL5

EN_ HP_CL4

BCKOFF4

BCKOFF3

BCKOFF2

BCKOFF1

0000,XXXX

16h

Timing Configuration

R/W

G

RSTR[1]

RSTR[0]

TSTART[1]

TSTART[0]

TFAULT[1]

TFAULT[0]

TDISC[1]

TDISC[0]

0000,0000

17h

Miscellaneous

Configuration 1

R/W

G

INT_EN

RSTR_EN

Reserved

Reserved

POFF_CL

CL_DISC

OUT_ISO

HP_TIME

1100,0000

PUSHBUTTONS

18h

Reserved

R/W

G

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

—

19h

Power Enable

WO

4321

PWR_OFF4

PWR_OFF3

PWR_OFF2

PWR_OFF1

PWR_ON4

PWR_ON3

PWR_ON2

PWR_ON1

0000,0000

1Ah

Global

WO

G

CLR_INT

Reserved

Reserved

RESET_IC

RESET_P4

RESET_P3

RESET_P2

RESET_P1

0000,0000

GENERAL

1Bh

ID

RO

G

ID_CODE[4]

ID_CODE[3]

ID_CODE[ 2]

ID_CODE[ 1] ID_

CODE[ 0] REV[2]

REV[1]

REV[0]

1100,0000

1Ch

SMODE and 2-Event

Enable

CoR

4321

EN4_CL6

EN3_CL6

EN2_CL6

EN1_CL6

SMODE4

SMODE3

SMODE2

SMODE1

0000,0000

1Dh

Reserved

—

G

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

—

1Eh

Watchdog

R/W

G

WDTIME[7]

WDTIME[6]

WDTIME[5]

WDTIME[4]

WDTIME[3]

WDTIME[2]

WDTIME[1]

WDTIME[0]

0000,0000

1Fh

Switch Mode

R/W

4321

EN_ WHDOG

WD_INT_EN

Reserved

Reserved

HWMODE4

HWMODE3

HWMODE2

HWMODE1

0000,0000

Table 37. Register Summary