Table 5. autoincrement rules – Rainbow Electronics MAX5965B User Manual

Page 26

MAX5965A/MAX5965B

High-Power, Quad, Monolithic, PSE Controllers

for Power over Ethernet

26

______________________________________________________________________________________

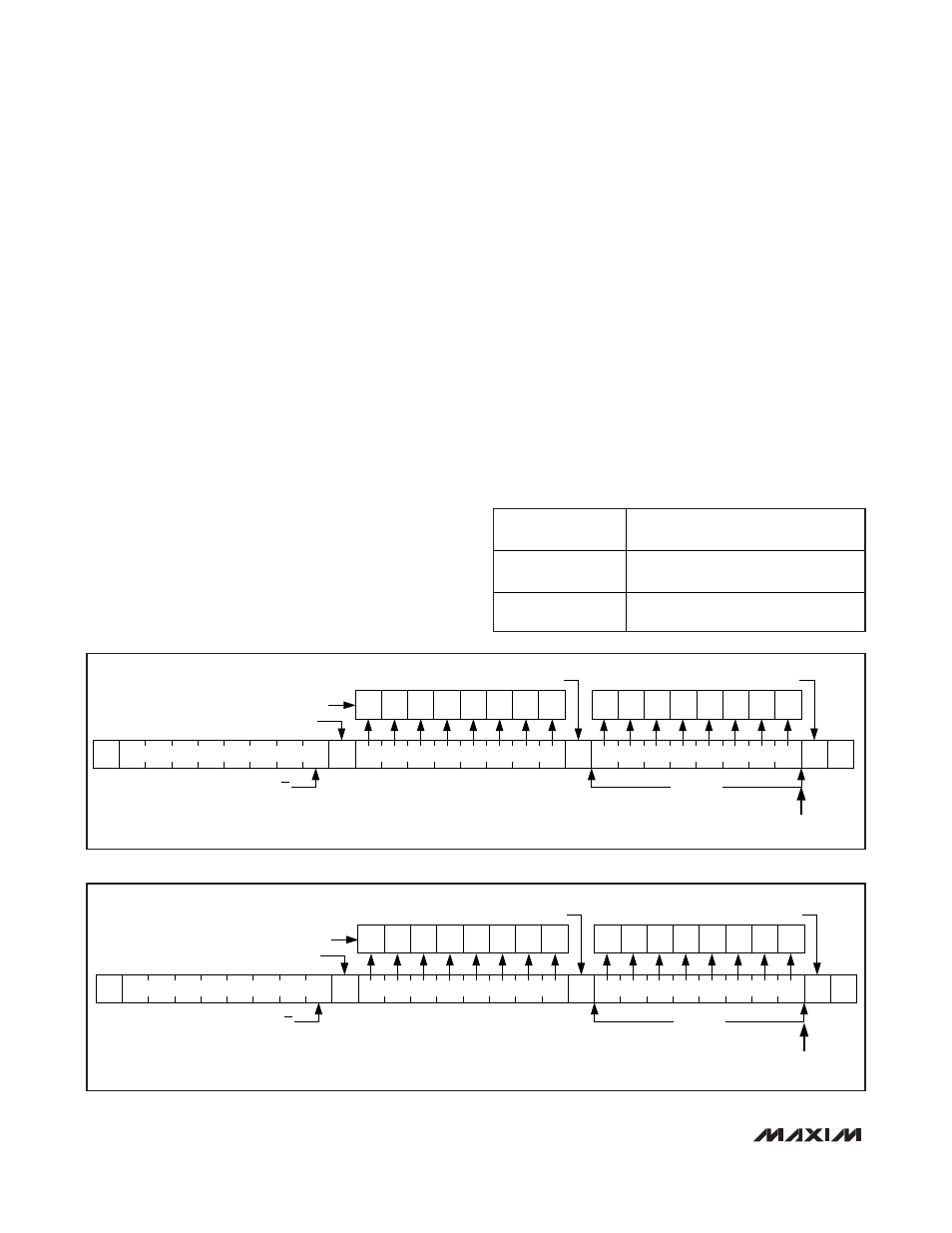

Message Format for Reading

The MAX5965A/MAX5965B read using the MAX5965A/

MAX5965B’s internally stored command byte as an

address pointer, the same way the stored command

byte is used as an address pointer for a write. The point-

er autoincrements after reading each data byte using the

same rules as for a write. Thus, a read is initiated by first

configuring the MAX5965A/MAX5965B’s command byte

by performing a write (Figure 11). The master now reads

‘n’ consecutive bytes from the MAX5965A/MAX5965B,

with the first data byte read from the register addressed

by the initialized command byte (Figure 12). When per-

forming read-after-write verification, remember to reset

the command byte’s address because the stored control

byte address autoincrements after the write.

Operation with Multiple Masters

When the MAX5965A/MAX5965B operate on a 2-wire

interface with multiple masters, a master reading the

MAX5965A/MAX5965B should use repeated starts

between the write which sets the MAX5965A/

MAX5965B’s address pointer, and the read(s) that take

the data from the location(s). It is possible for master 2 to

take over the bus after master 1 has set up the

MAX5965A/MAX5965B’s address pointer but before mas-

ter 1 has read the data. If master 2 subsequently resets

the MAX5965A/MAX5965B’s address pointer then master

1’s read may be from an unexpected location.

Command Address Autoincrementing

Address autoincrementing allows the MAX5965A/

MAX5965B to be configured with fewer transmissions

by minimizing the number of times the command

address needs to be sent. The command address

stored in the MAX5965A/MAX5965B generally incre-

ments after each data byte is written or read (Table 5).

The MAX5965A/MAX5965B are designed to prevent

overwrites on unavailable register addresses and unin-

tentional wrap-around of addresses.

Figure 11. Control and Single Data Byte Received

S

A

A

A

P

0

SLAVE ADDRESS

CONTROL BYTE

DATA BYTE

ACKNOWLEDGE FROM THE

MAX5965A/MAX5965B

1 BYTE

AUTOINCREMENT

MEMORY WORD ADDRESS

D15 D14 D13 D12 D11 D10

D9

D8

D1

D0

D3

D2

D5

D4

D7

D6

HOW CONTROL BYTE AND DATA BYTE MAP

INTO THE REGISTER

ACKNOWLEDGE FROM THE

MAX5965A/MAX5965B

ACKNOWLEDGE FROM THE

MAX5965A/MAX5965B

R/W

Figure 12. ‘n’ Data Bytes Received

S

A

A

A

P

0

SLAVE ADDRESS

CONTROL BYTE

DATA BYTE

ACKNOWLEDGE FROM THE

MAX5965A/MAX5965B

n BYTES

AUTOINCREMENT

MEMORY WORD ADDRESS

D15 D14 D13 D12 D11 D10

D9

D8

D1

D0

D3

D2

D5

D4

D7

D6

HOW CONTROL BYTE AND DATA BYTE MAP

INTO THE REGISTER

ACKNOWLEDGE FROM THE

MAX5965A/MAX5965B

ACKNOWLEDGE FROM THE

MAX5965A/MAX5965B

R/W

Table 5. Autoincrement Rules

COMMAND BYTE

ADDRESS RANGE

AUTOINCREMENT BEHAVIOR

0x00 to 0x26

Command address autoincrements

after byte read or written

0x26

Command address remains at 0x26

after byte written or read