Table 25. smode and 2-event enable register, Table 26. watchdog register – Rainbow Electronics MAX5965B User Manual

Page 38

MAX5965A/MAX5965B

High-Power, Quad, Monolithic, PSE Controllers

for Power over Ethernet

38

______________________________________________________________________________________

Enable 2-event classification for a port by setting the corre-

sponding ENx_CL6 bit (Table 25). When the bit is enabled,

the classification cycle will be repeated three times at

21.3ms intervals. The device keeps the output voltage

around -9V between each cycle. The repetition of the clas-

sification cycles enables discovering of class 6 PDs. The

ENx_CL6 bit is active only in auto- or semi-mode.

Note: Performing three consecutive classifications in

manual mode is not the same as performing 2-event

classification in semi or auto mode.

Enable the SMODE function (Table 25) by setting

EN_WHDOG (R1Fh[7]) to 1. The SMODE_ bit goes high

when the watchdog counter reaches zero and the

port(s) switch over to hardware-controlled mode.

SMODE_ also goes high each and every time the soft-

ware tries to power on a port, but is denied since the

port is in hardware mode. A reset sets R1Ch = 00h.

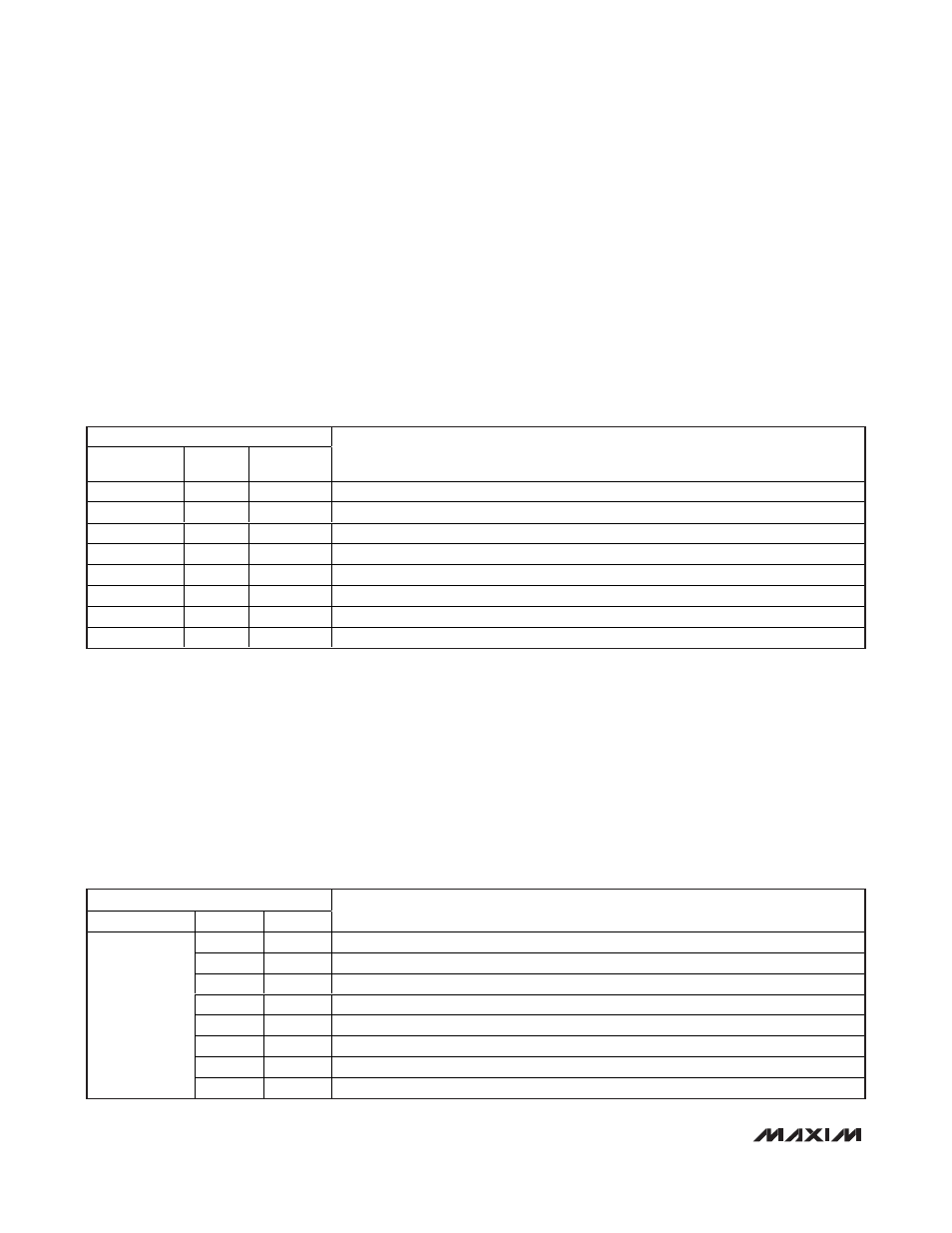

Table 25. SMODE and 2-Event Enable Register

ADDRESS = 1Ch

SYMBOL

BIT

CoR or

R/W

DESCRIPTION

EN4_CL6

7

R/W

Port 4 2-event classification enabled

EN3_CL6

6

R/W

Port 3 2-event classification enabled

EN2_CL6

5

R/W

Port 2 2-event classification enabled

EN1_CL6

4

R/W

Port 1 2-event classification enabled

SMODE4

3

CoR

Port 4 hardware control flag

SMODE3

2

CoR

Port 3 hardware control flag

SMODE2

1

CoR

Port 2 hardware control flag

SMODE1

0

CoR

Port 1 hardware control flag

Table 26. Watchdog Register

ADDRESS = 1Eh

SYMBOL

BIT

R/W

DESCRIPTION

7

R/W

WDTIME[7]

6

R/W

WDTIME[6]

5

R/W

WDTIME[5]

4

R/W

WDTIME[4]

3

R/W

WDTIME[3]

2

R/W

WDTIME[2]

1

R/W

WDTIME[1]

WDTIME

0

R/W

WDTIME[0]

Set EN_WHDOG (R1Fh[7]) to 1 to enable the watchdog

function. When activated, the watchdog timer counter,

WDTIME[7:0], continuously decrements toward zero

once every 164ms. Once the counter reaches zero

(also called watchdog expiry), the MAX5965A/

MAX5965B enter hardware-controlled mode and each

port shifts to a mode set by the HWMODE_ bit in regis-

ter R1Fh (Table 27). Use software to set WDTIME

(Table 26) and continuously set this register to some

nonzero value before the register reaches zero to pre-

vent a watchdog expiry. In this way, the software grace-

fully manages the power to ports upon a system crash

or switchover.

While in hardware-controlled mode, the MAX5965A/

MAX5965B ignore all requests to turn the power on and

the flag SMODE_ indicates that the hardware has taken

control of the MAX5965A/MAX5965B operation. In addi-

tion, the software is not allowed to change the mode of

operation in hardware-controlled mode. A reset sets

R1Eh = 00h.