Rainbow Electronics MAX5965B User Manual

Page 18

MAX5965A/MAX5965B

High-Power, Quad, Monolithic, PSE Controllers

for Power over Ethernet

18

______________________________________________________________________________________

Powered Device Classification

(PD Classification)

During the PD classification mode, the MAX5965A/

MAX5965B force a probe voltage (-18V) at DET_ and

measure the current into DET_. The measured current

determines the class of the PD.

After each classification cycle, the device sets the

CL_END_ bit (R04h/05h[7:4]) high and reports the clas-

sification results in the status registers R0Ch[6:4],

R0Dh[6:4], R0Eh[6:4], and R0Fh[6:4]. The CL_END_ bit

is reset to low when read through register R05h or after

a port reset. Both status registers, R04h, and R05h are

cleared after the port powers down. Table 2 shows the

IEEE 802.3af requirement for a PSE classifying a PD at

the power interface (PI).

The MAX5965A/MAX5965B support high power beyond

the IEEE 802.3af standard by providing additional clas-

sifications (Class 5 and 2-event classification).

Class 5 PD Classification

During classification, if the MAX5965A/MAX5965B

detect currents in excess of I

CLASS

> 48mA, then the

PD will be classified as a Class 5 powered device.

Status registers R0Ch[6:4] or R0Dh[6:4] or R0Eh[6:4] or

R0Fh[6:4] will report the Class 5 classification result.

2-Event (Class 6) PD Classification

When 2-event classification is activated, the classifica-

tion cycle is repeated three times with 8ms wait time

between each cycle (see Figure 1b). Between each

classification cycle, the MAX5965A/MAX5965B do not

reset the port voltage completely but keeps the output

voltage at -9V. The EN_CL6 bits in R1Ch[7:4] enable 2-

event classification on a per port basis.

Powered State

When the MAX5965A/MAX5965B enter a powered

state, the t

START

and t

DISC

timers are reset. Before

turning on the port power, the MAX5965A/MAX5965B

check if any other port is not turning on and if the

t

FAULT

timer is zero. Another check is performed if the

ACD_EN bit is set, in this case the OSC_FAIL bit must

be low (oscillator is okay) for the port to be powered.

If these conditions are met, the MAX5965A/MAX5965B

enter startup where it turns on power to the port. An

internal signal, POK_, asserts high when V

OUT

is within

2V from V

EE

. PGOOD_ status bits are set high if POK_

stays high longer than t

PGOOD

. PGOOD immediately

resets when POK goes low (see Figure 2).

The PG_CHG_ bit sets when a port powers up or down.

PWR_EN sets when a port powers up and resets when a

port shuts down. The port shutdown timer lasts 0.5ms

and prevents other ports from turning off during that peri-

od, except in the case of emergency shutdowns (RESET

= L, RESET_IC = H, V

EEUVLO,

V

DDUVLO,

and TSHD).

The MAX5965A/MAX5965B always check the status of

all ports before turning off. A priority logic system deter-

mines the order to prevent the simultaneous turn-on or

turn-off of the ports. The port with the lesser ordinal

number gets priority over the others (i.e., port 1 turns on

first, port 2 second, port 3 third, and port 4 fourth).

Setting PWR_OFF_ high turns off power to the corre-

sponding port.

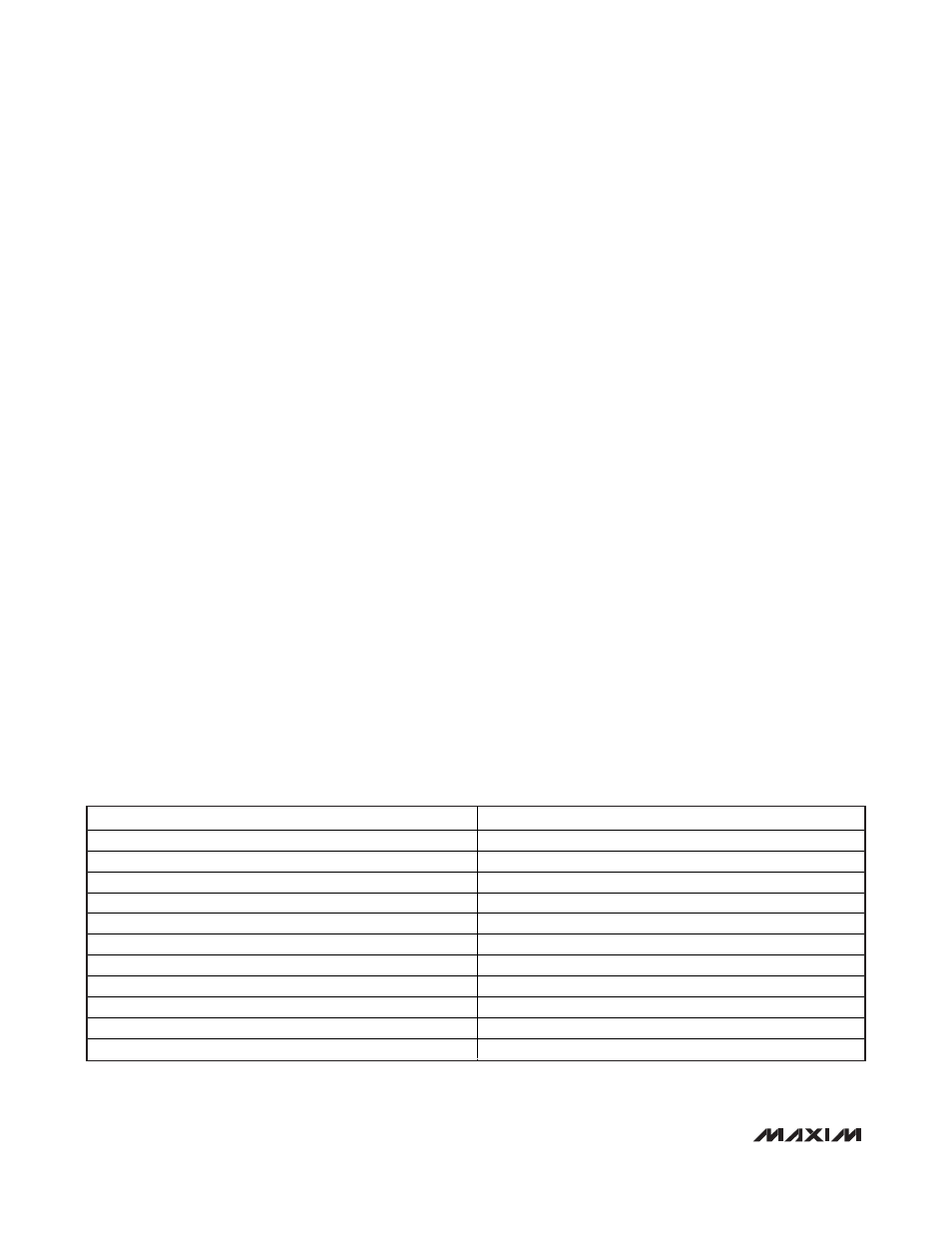

Table 2. PSE Classification of a PD (Table 33-4 of the IEEE 802.3af)

MEASURED I

CLASS

(mA)

CLASSIFICATION

0 to 5

Class 0

> 5 and < 8

May be Class 0 and 1

8 to 13

Class 1

> 13 and < 16

May be Class 1 or 2

16 to 21

Class 2

> 21 and < 25

May be Class 2 or 3

25 to 31

Class 3

> 31 and < 35

May be Class 3 or 4

35 to 45

Class 4

> 45 and < 51

May be Class 4 or 5

51 to 68

Class 5