Rainbow Electronics MAX5965B User Manual

Page 17

MAX5965A/MAX5965B

High-Power, Quad, Monolithic, PSE Controllers

for Power over Ethernet

______________________________________________________________________________________

17

A valid PD has a 25kΩ discovery signature characteristic

as specified in the IEEE 802.3af/at standard. Table 1

shows the IEEE 802.3af/at specification for a PSE detect-

ing a valid PD signature. See the

Typical Operating

Circuits

and Figure 1a (Detection, Classification, and

Power-Up Port Sequence). The MAX5965A/MAX5965B

can probe and categorize different types of devices con-

nected to the port such as: a valid PD, an open circuit, a

low resistive load, a high resistive load, a high capacitive

load, a positive DC supply, or a negative DC supply.

During detection, the MAX5965A/MAX5965B keep the

external MOSFET off and force two probe voltages

through the DET_ input. The current through the DET_

input is measured as well as the voltage at OUT_. A

two-point slope measurement is used as specified by

the IEEE 802.3af standard to verify the device connect-

ed to the port. The MAX5965A/MAX5965B implement

appropriate settling times and a 100ms digital integra-

tion to reject 50Hz/60Hz power-line noise coupling.

An external diode, in series with the DET_ input, restricts

PD detection to the first quadrant as specified by the

IEEE 802.3af/at standard. To prevent damage to non-PD

devices, and to protect themselves from an output short

circuit, the MAX5965A/MAX5965B limit the current into

DET_ to less than 2mA maximum during PD detection.

In midspan mode, the MAX5965A/MAX5965B wait 2.2s

before attempting another detection cycle after every

failed detection. The first detection, however, happens

immediately after issuing the detection command.

High-Capacitance Detection

The CLC_EN bit in register R23h[5] enables the large

capacitor detection feature for legacy PD devices.

When CLC_EN = 1, the high-capacitance detection limit

is extended up to 150µF. CLC_EN = 0 is the default

condition for the normal capacitor size detection. See

Table 1 and the

Register Map and Description

section.

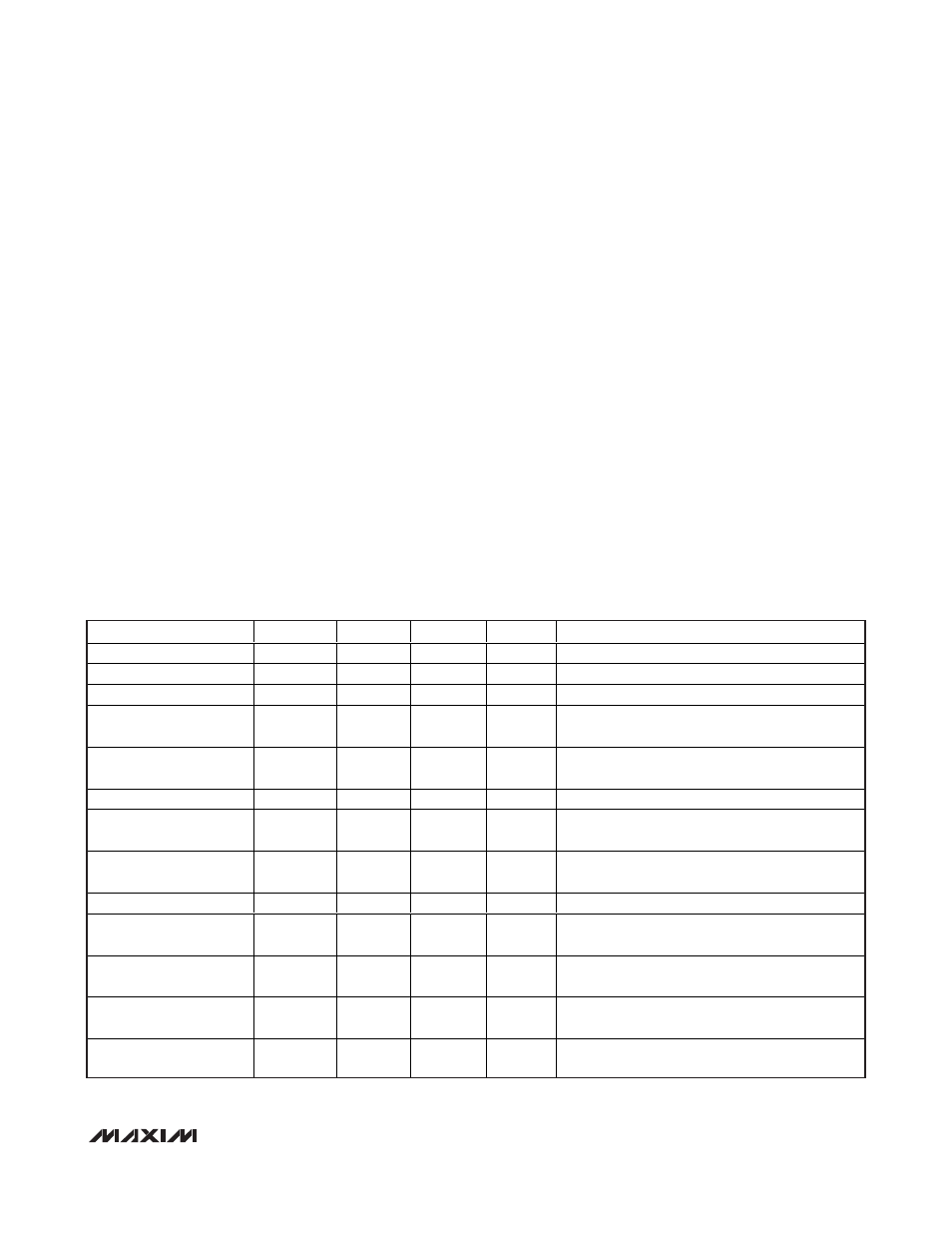

Table 1. PSE PI Detection Modes Electrical Requirement

(Table 33-2 of the IEEE 802.3af Standard)

PARAMETER

SYMBOL

MIN

MAX

UNITS

ADDITIONAL INFORMATION

Open-Circuit Voltage

V

OC

—

30

V

In detection mode only

Short-Circuit Current

I

SC

—

5

mA

In detection mode only

Valid Test Voltage

V

VALID

2.8

10

V

Voltage Difference

Between Test Points

ΔV

TEST

1

—

V

Time Between Any Two

Test Points

t

BP

2

—

ms

This timing implies a 500Hz maximum probing

frequency

Slew Rate

V

SLEW

0.1

V/µs

Accept Signature

Resistance

R

GOOD

19

26.5

k

Ω

Reject Signature

Resistance

R

BAD

< 15

> 33

k

Ω

Open-Circuit Resistance

R

OPEN

500

—

k

Ω

Accept Signature

Capacitance

C

GOOD

—

150

nF

Reject Signature

Capacitance

C

BAD

10

—

µF

Signature Offset Voltage

Tolerance

V

OS

0

2.0

V

Signature Offset Current

Tolerance

I

OS

0

12

µA