Register map and description, Table 6. interrupt register, Table 7. interrupt mask register – Rainbow Electronics MAX5965B User Manual

Page 27

MAX5965A/MAX5965B

High-Power, Quad, Monolithic, PSE Controllers

for Power over Ethernet

______________________________________________________________________________________

27

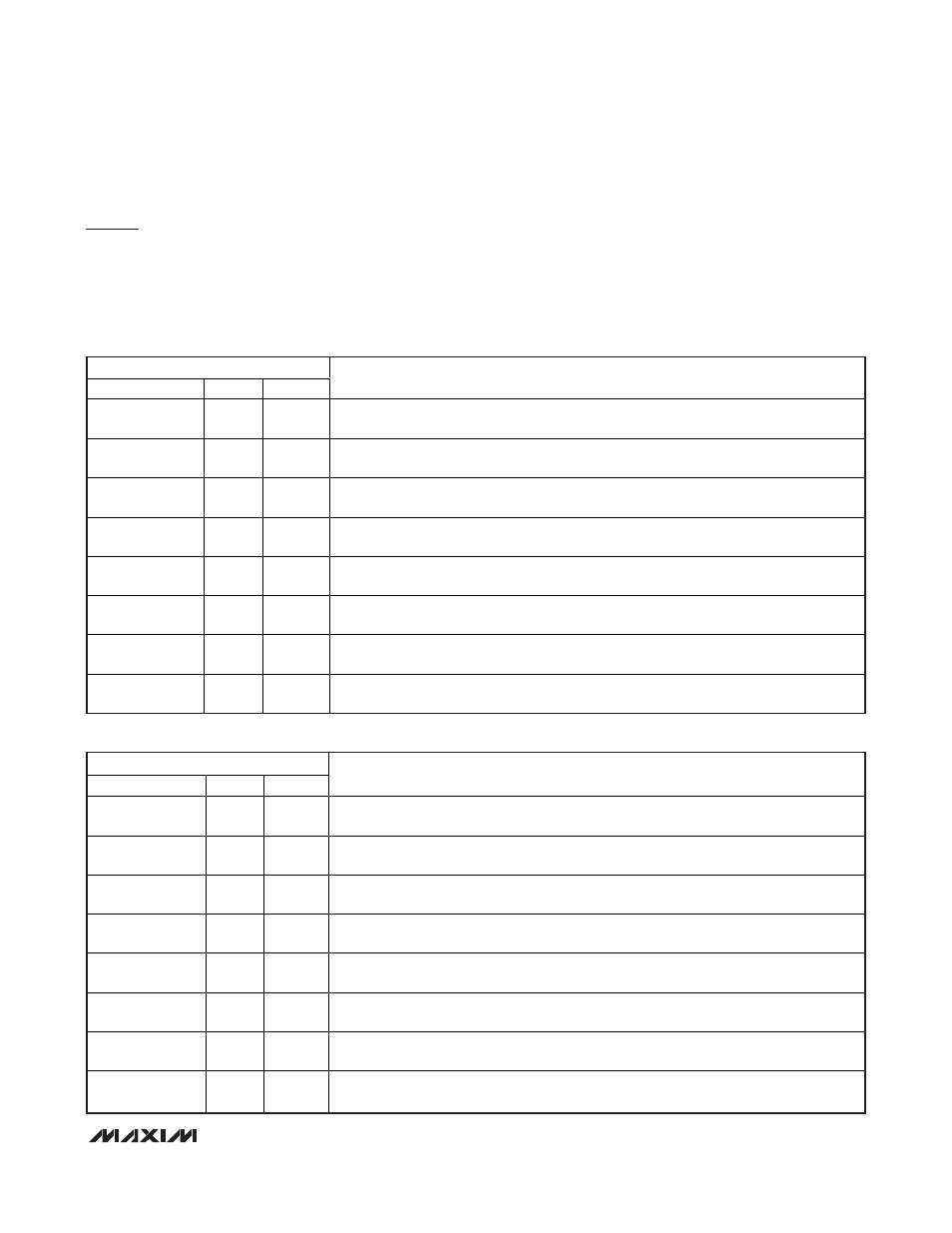

Table 6. Interrupt Register

ADDRESS = 00h

SYMBOL

BIT

R/W

DESCRIPTION

SUP_FLT

7

R

Interrupt signal for supply faults. SUP_FLT is the logic OR of all the bits [7:0] in register

R0Ah/R0Bh (Table 12).

TSTR_FLT

6

R

Interrupt signal for startup failures. TSTR_FLT is the logic OR of bits [7:0] in register

R08h/R09h (Table 11).

IMAX_FLT

5

R

Interrupt signal for current-limit violations. IMAX_FLT is the logic OR of bits [3:0] in register

R06h/R07h (Table 10).

CL_END

4

R

Interrupt signal for completion of classification. CL_END is the logic OR of bits [7:4] in

register R04h/R05h (Table 9).

DET_END

3

R

Interrupt signal for completion of detection. DET_END is the logic OR of bits [3:0] in

register R04h/R05h (Table 9).

LD_DISC

2

R

Interrupt signal for load disconnection. LD_DISC is the logic OR of bits [7:4] in register

R06h/R07h (Table 10).

PG_INT

1

R

Interrupt signal for PGOOD status change. PG_INT is the logic OR of bits [7:4] in register

R02h/R03h (Table 8).

PE_INT

0

R

Interrupt signal for power-enable status change. PEN_INT is the logic OR of bits [3:0] in

register R02h/R03h (Table 8).

Table 7. Interrupt Mask Register

ADDRESS = 01h

SYMBOL

BIT

R/W

DESCRIPTION

MASK7

7

R/W

Interrupt mask bit 7. A logic-high enables the SUP_FLT interrupts. A logic-low disables the

SUP_FLT interrupts.

MASK6

6

R/W

Interrupt mask bit 6. A logic-high enables the TSTR_FLT interrupts. A logic-low disables

the TSTR_FLT interrupts.

MASK5

5

R/W

Interrupt mask bit 5. A logic-high enables the IMAX_FLT interrupts. A logic-low disables

the IMAX_FLT interrupts.

MASK4

4

R/W

Interrupt mask bit 4. A logic-high enables the CL_END interrupts. A logic-low disables the

CL_END interrupts.

MASK3

3

R/W

Interrupt mask bit 3. A logic-high enables the DET_END interrupts. A logic-low disables the

DET_END interrupts.

MASK2

2

R/W

Interrupt mask bit 2. A logic-high enables the LD_DISC interrupts. A logic-low disables the

LD_DISC interrupts.

MASK1

1

R/W

Interrupt mask bit 1. A logic-high enables the PG_INT interrupts. A logic-low disables the

PG_INT interrupts.

MASK0

0

R/W

Interrupt mask bit 0. A logic-high enables the PEN_INT interrupts. A logic-low disables the

PEN_INT interrupts.

Register Map and Description

The interrupt register (Table 6) summarizes the event

register status and is used to send an interrupt signal

(INT goes low) to the controller. Writing a 1 to R1Ah[7]

clears all interrupt and events registers. A reset sets

R00h to 00h.

INT_EN (R17h[7]) is a global interrupt mask (Table 7).

The MASK_ bits activate the corresponding interrupt

bits in register R00h. Writing a 0 to INT_EN (R17h[7])

disables the INT output.

A reset sets R01h to AAA00A00b where A is the state of

the AUTO input prior to the reset.