Table 35b. class sequence states (continued), Table 36. current registers – Rainbow Electronics MAX5965B User Manual

Page 43

MAX5965A/MAX5965B

High-Power, Quad, Monolithic, PSE Controllers

for Power over Ethernet

______________________________________________________________________________________

43

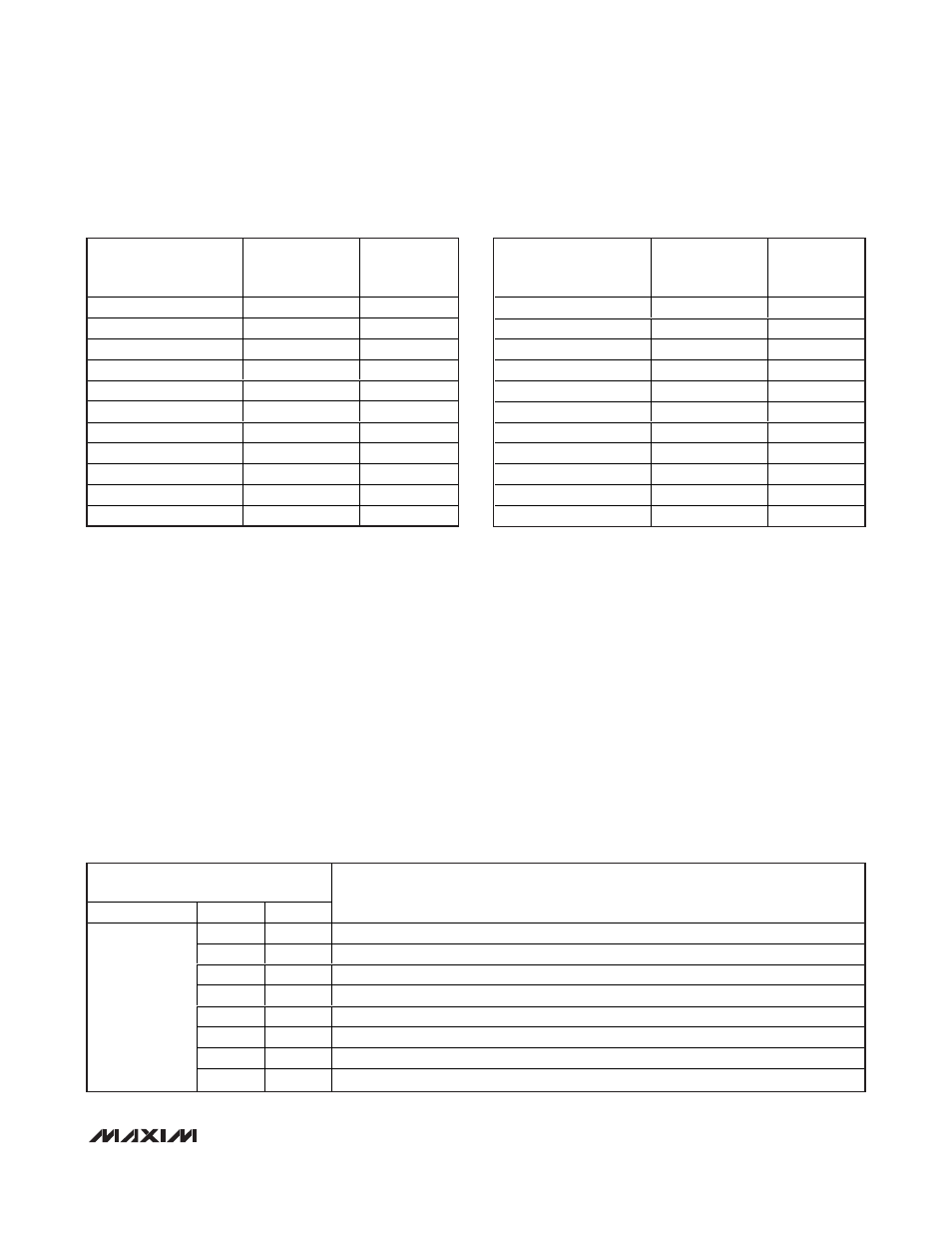

Table 35b. Class Sequence States (continued)

CLASS_[5:0]

(ADDRESS = 2Ch, 2Dh,

2Eh, 2Fh)

CLASS

SEQUENCE

ICUT[2:0]

101010

Illegal

000

101011

Illegal

000

101100

Illegal

000

101101

Illegal

000

101110

Illegal

000

101111

Illegal

000

110000

Reserved

000

110001

Reserved

000

110010

Reserved

000

110011

Reserved

000

110100

Reserved

000

CLASS_[5:0]

(ADDRESS = 2Ch, 2Dh,

2Eh, 2Fh)

CLASS

SEQUENCE

ICUT[2:0]

110101

Reserved

000

110110

Reserved

000

110111

Reserved

000

111000

Reserved

000

111001

Reserved

000

111010

Reserved

000

111011

Reserved

000

111100

Reserved

000

111101

Reserved

000

111110

Reserved

000

111111

Reserved

000

ADDRESS = 30h, 31h, 32h, 33h, 34h,

35h, 36h, 37h

SYMBOL

BIT

R/W

DESCRIPTION

7

W

IPD_[8]

6

W

IPD_[7]

5

W

IPD_[6]

4

W

IPD_[5]

3

W

IPD_[4]

2

W

IPD_[3]

1

W

IPD_[2]

IPD_

0

W

IPD_[1]/IPD_[0]

Table 36. Current Registers

When the ENx_CL6 (R1Ch[7:4]) bits are set, 2-event

classification is enabled. Classification is repeated

three times and the classification results are set

according to Table 35b.

A Class 6 PD is defined by any sequence of the type

[00x, 0x0, 0xx, x00, x0x, xx0] where ‘x’ can be 1, 2, 3,

4, or 5. All sequences made by the same class result

define the class itself (for example, 222 defines Class

2). Any other sequence will be considered illegal and

coded as 101—-. For example, a sequence 232 or 203

will be illegal. The illegal sequences all default to class

0. A reset or power-up sets R2Ch = R2Dh = R2Eh =

R2Fh = 00h.

The MAX5965A/MAX5965B provide current readout for

each port during classification and normal power

mode. The current per port information is separated

into 9 bits. They are organized into two consecutive

registers for each one of the ports. The information can

be quickly retrieved using the autoincrement option of

the address pointer. To avoid the LSB register chang-

ing while reading the MSB, the information is frozen

once the addressing byte points to any of the current

readout registers.

During power mode, the current value can be calculat-

ed as

I

PORT

= N

IPD_

x 1.953125mA

During classification, the current is

I

CLASS

= N

IPD_

x 0.0975mA

where N

IPD_

is the decimal value of the 9-bit word. The

ADC saturates both at full scale and at zero. A reset

sets R30h to R37h = 00h.