Table 8. power event register, Table 9. detect event register – Rainbow Electronics MAX5965B User Manual

Page 28

MAX5965A/MAX5965B

High-Power, Quad, Monolithic, PSE Controllers

for Power over Ethernet

28

______________________________________________________________________________________

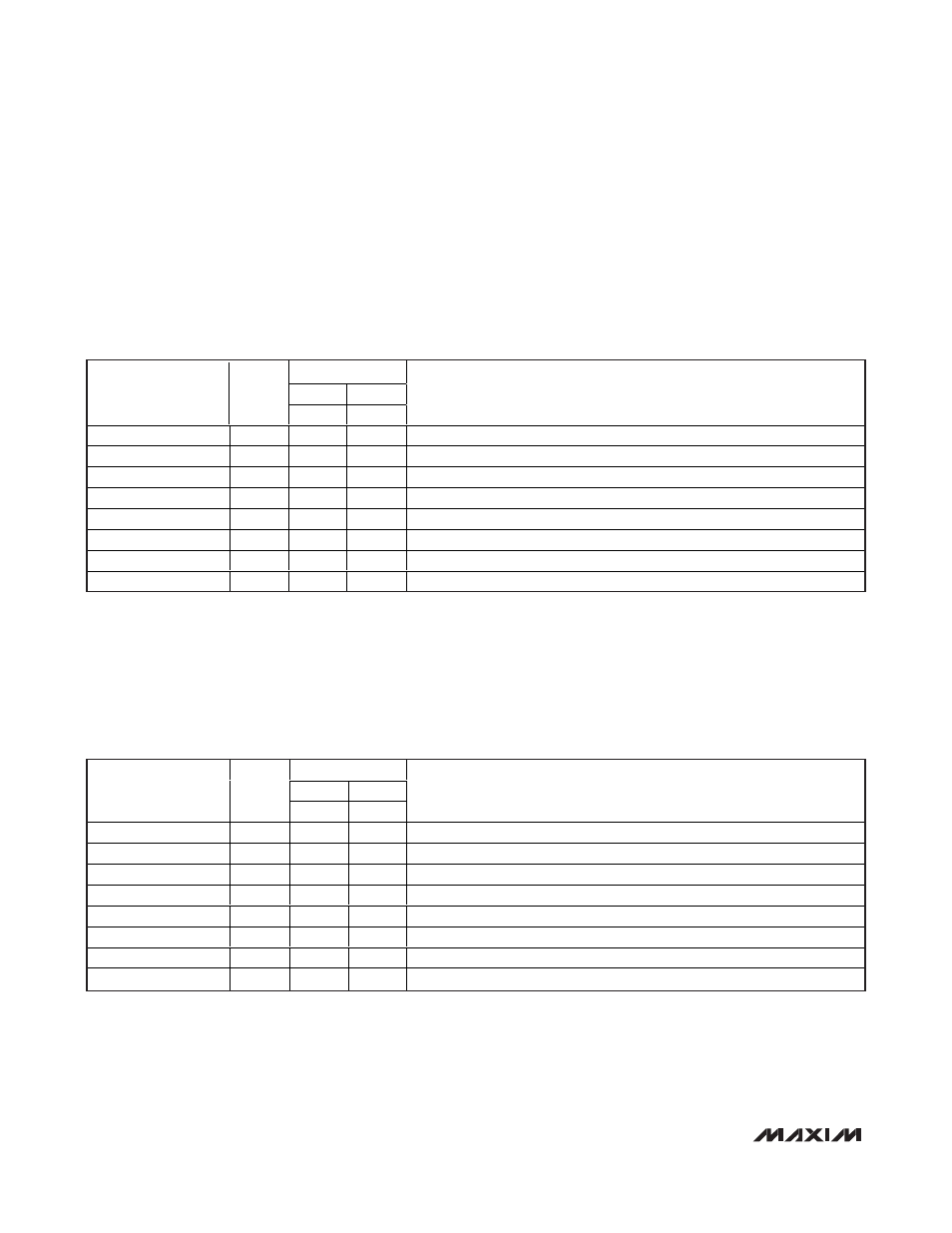

The power event register (Table 8) records changes in

the power status of the four ports. Any change in

PGOOD_ (R10h[7:4]) sets PG_CHG_ to 1. Any change

in the PWR_EN_ (R10h[3:0]) sets PWEN_CHG_ to 1.

PG_CHG_ and PWEN_CHG_ trigger on the edges of

PGOOD_ and PWR_EN_ and do not depend on the

actual level of the bits. The power event register has

two addresses. When read through the R02h address,

the content of the register is left unchanged. When read

through the CoR R03h address, the register content is

cleared. A reset sets R02h/R03h = 00h.

Table 8. Power Event Register

ADDRESS

02h

03h

SYMBOL

BIT

R/W

R/W

DESCRIPTION

PG_CHG4

7

R

CoR

PGOOD change event for port 4

PG_CHG3

6

R

CoR

PGOOD change event for port 3

PG_CHG2

5

R

CoR

PGOOD change event for port 2

PG_CHG1

4

R

CoR

PGOOD change event for port 1

PWEN_CHG4

3

R

CoR

Power enable change event for port 4

PWEN_CHG3

2

R

CoR

Power enable change event for port 3

PWEN_CHG2

1

R

CoR

Power enable change event for port 2

PWEN_CHG1

0

R

CoR

Power enable change event for port 1

Table 9. Detect Event Register

ADDRESS

04h

05h

SYMBOL

BIT

R/W

R/W

DESCRIPTION

CL_END4

7

R

CoR

Classification completed on port 4

CL_END3

6

R

CoR

Classification completed on port 3

CL_END2

5

R

CoR

Classification completed on port 2

CL_END1

4

R

CoR

Classification completed on port 1

DET_END4

3

R

CoR

Detection completed on port 4

DET_END3

2

R

CoR

Detection completed on port 3

DET_END2

1

R

CoR

Detection completed on port 2

DET_END1

0

R

CoR

Detection completed on port 1

DET_END_/CL_END_ is set high whenever detection/

classification is completed on the corresponding port. A

1 in any of the CL_END_ bits forces R00h[4] to 1. A 1 in

any of the DET_END_ bits forces R00h[3] to 1. As with

any of the other events register, the detect event register

has two addresses. When read through the R04h

address, the content of the register is left unchanged.

When read through the CoR R05h address, the register

content is cleared. A reset sets R04h/R05h = 00h.