28 mode bit reset (ffh), Mode bit reset (ffh) – Rainbow Electronics W25Q32 User Manual

Page 45

W25Q80, W25Q16, W25Q32

Publication Release Date: June 20, 2007

- 45 - Advanced - Revision A5

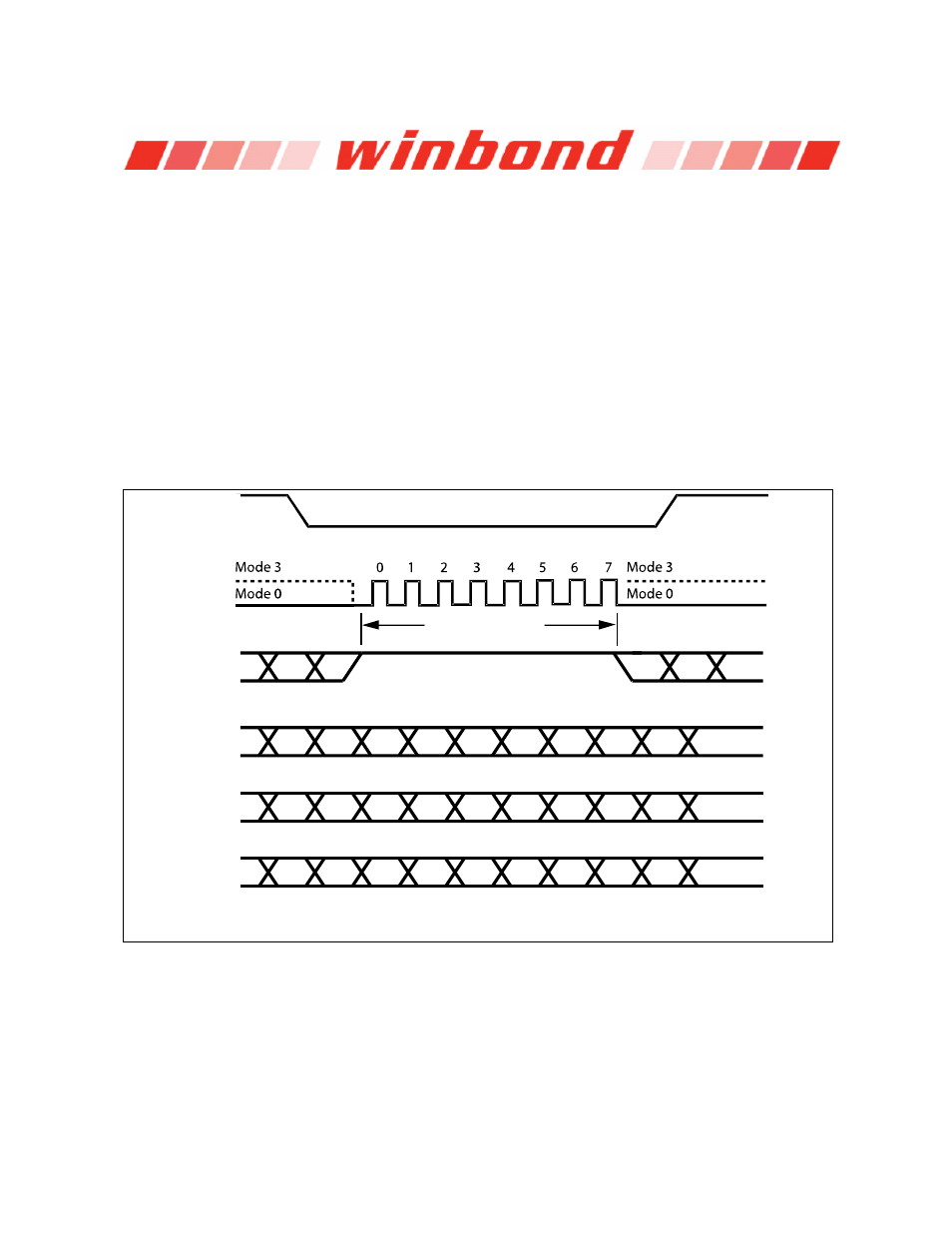

10.2.28 Mode Bit Reset (FFh)

For Fast Read Dual/Quad I/O operations, Mode Bits (M7-0) are implemented to further reduce

instruction overhead. By setting the Mode Bits (M7-0) to “Ax” hex, the next Fast Read Dual/Quad I/O

operation does not require the BBh/EBh instruction code (See 10.2.12 Fast Read Dual I/O and 10.2.13

Fast Read Quad I/O for detail descriptions).

If the system controller is Reset during operation it will likely send a standard SPI instruction, such

as Read ID (9Fh) or Fast Read (0Bh), to the 25Q16/32/80. However, as with most SPI Serial Flash

memories, the 25Q80/16/32 does not have a hardware Reset pin, so if Mode bits are set to “Ax”

hex, the 25Q80/16/32 will not recognize any standard SPI instructions.

To address this possibility, it is

recommended to issue a Mode Bit Reset instruction “FFh” as the first instruction after a system Reset.

Doing so will release the Mode Bits for the “Ax” hex state and allow Standard SPI instructions to be

recognized. The Mode Bits Reset instruction is shown in figure 29.

Figure 29. Mode Bit Reset for Fast Read Dual/Quad I/O

IO

0

/CS

CLK

IO

1

Instruction (FFh)

IO

2

Don’t Care

IO

3

Don’t Care

Don’t Care