12 fast read dual i/o (bbh), Fast read dual i/o (bbh) – Rainbow Electronics W25Q32 User Manual

Page 28

W25Q80, W25Q16, W25Q32

- 28 -

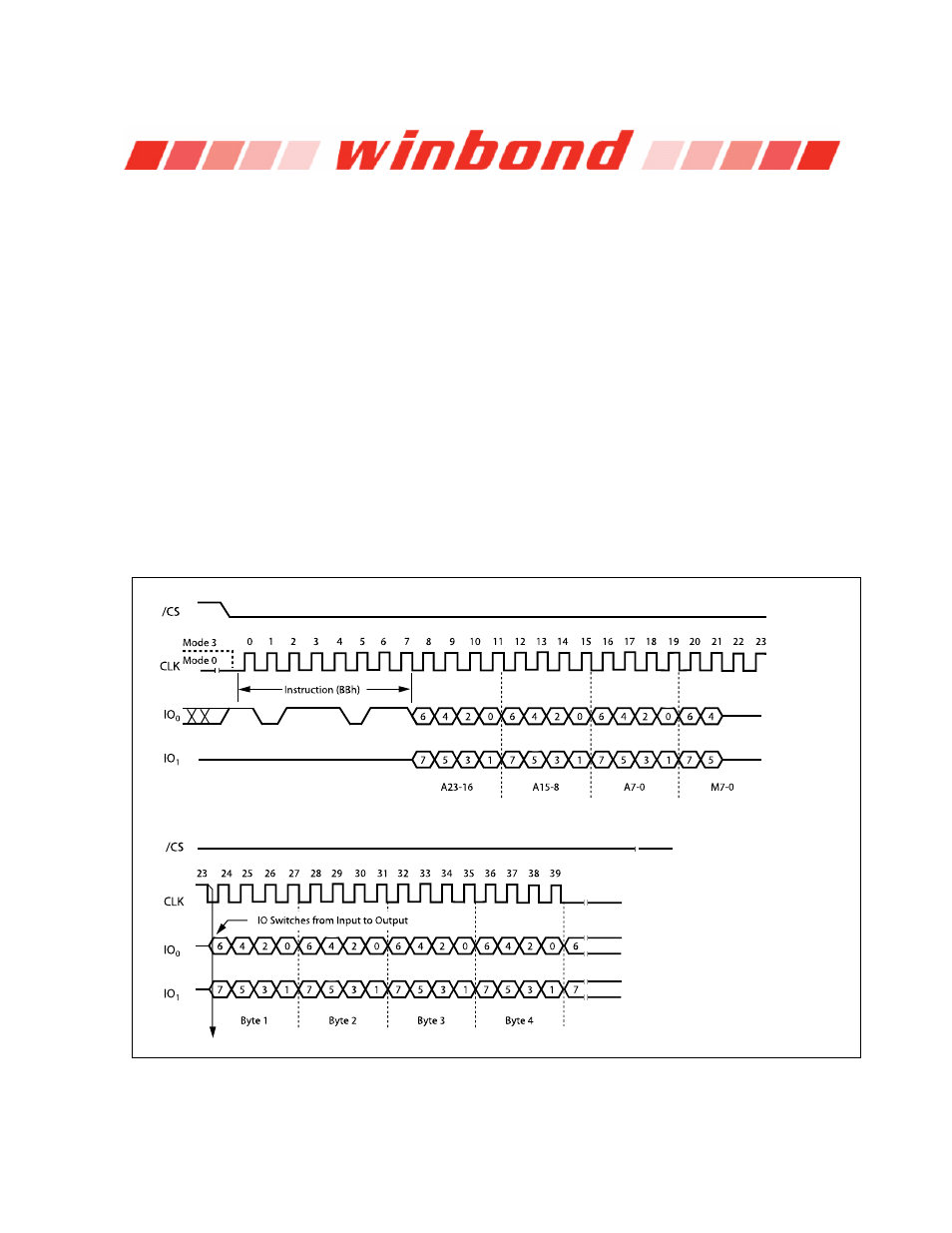

10.2.12 Fast Read Dual I/O (BBh)

The Fast Read Dual I/O (BBh) instruction allows for improved random access while maintaining two IO

pins, IO

0

and IO

1

. It is similar to the Fast Read Dual Output (3Bh) instruction but with the capability to

input the Address bits (A23-0) two bits per clock. This reduced instruction overhead may allow for code

execution (XIP) directly from the Dual SPI in some applications. To ensure optimum performance the

High Performance Mode (HPM) instruction (A3h) must be executed once, prior to the Fast Read Dual

I/O Instruction.

The Fast Read Dual I/O instruction can further reduce instruction overhead through setting the Mode

bits (M7-0) after the input Address bits (A23-0), as shown in figure 12a. The upper nibble of the Mode

(M7-4) controls the length of the next Fast Read Dual I/O instruction through the inclusion or exclusion

of the first byte instruction code. The lower nibble bits of the Mode (M3-0) are don’t care (“x”). However,

the IO pins should be high-impedance prior to the falling edge of the first data out clock.

If the Mode bits (M7-0) equals “Ax” hex, then the next Fast Read Dual I/O instruction (after /CS is raised

and then lowered) does not require the BBh instruction code, as shown in figure 12b.. This reduces the

instruction sequence by eight clocks and allows the address to be immediately entered after /CS is

asserted low. If the Mode bits (M7-0) are any value other than “Ax” hex, the next instruction (after /CS is

raised and then lowered) requires the first byte instruction code, thus returning to normal operation. A

Mode Bit Reset instruction can be used to reset Mode Bits (M7-0) before issuing normal instructions

(See 10.2.28 for detailed descriptions).

Figure 12a. Fast Read Dual Input/Output Instruction Sequence Diagram (M7-0 = 0xh or NOT Axh)