C control channel, Uart – Rainbow Electronics MAX9258 User Manual

Page 35

sent, but since CTO timed out, bypass mode ends and

base mode is active for the next vertical blanking period.

With STO > CTO > ETO, bypass mode can be made

continuous by having the ECU send real commands or

dummy commands (such as a command to a nonexist-

ing address) each time the control channel opens.

Then the ECU does not have to send a command to

enter bypass mode each time it wants to program the

peripheral device.

UART

UART Frame Format

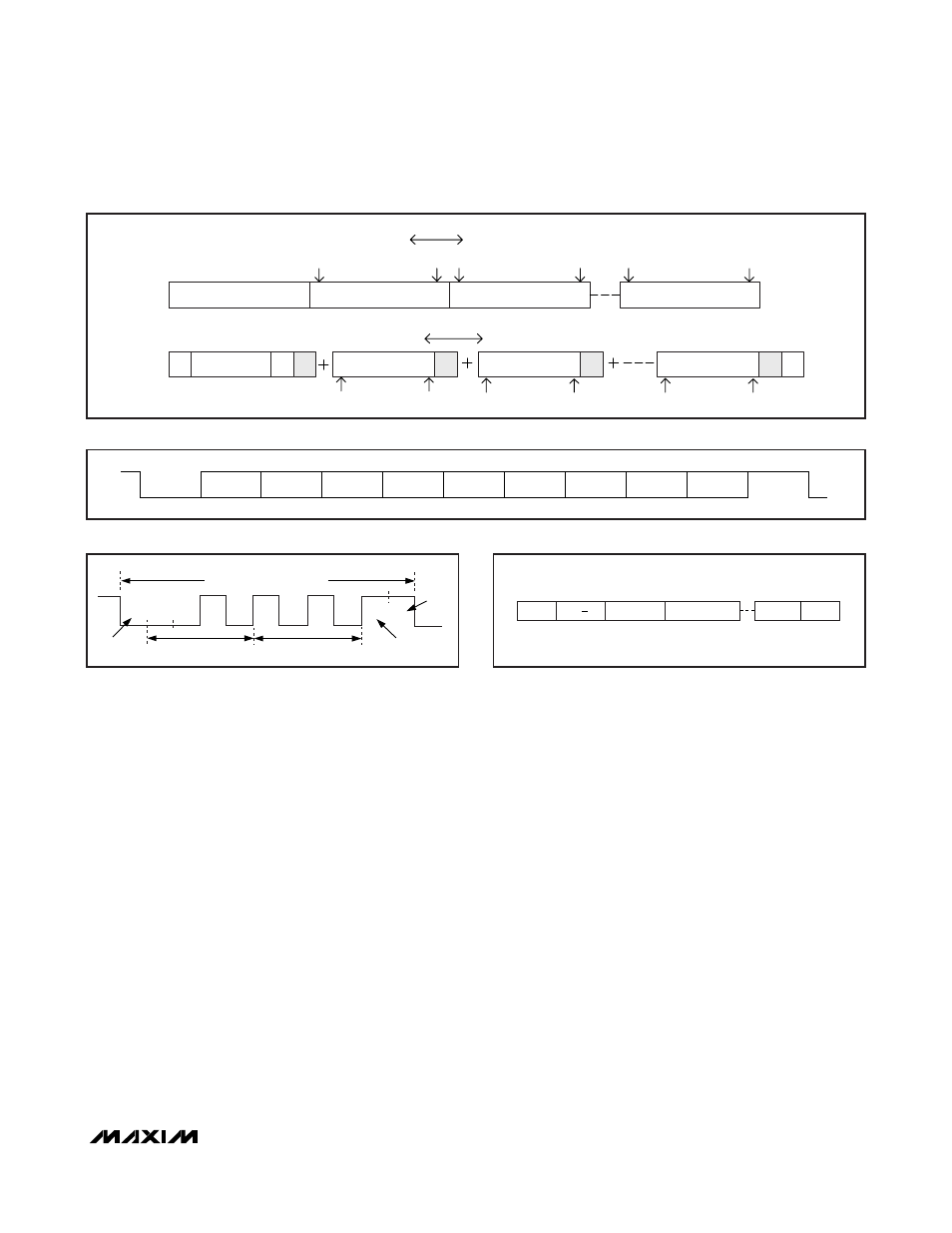

The UART frame used to program the MAX9257 and

the MAX9258 has a low start bit, eight data bits, an

even parity bit and a high stop bit. The data following

the start bit is the LSB. With even parity, when there are

an odd number of 1s in the data bits (D0 through D7)

the parity bit is set to 1. The stop bit is sampled and if it

is not high, a frame error is generated (Figure 26).

UART Synchronization Frame

The synchronization frame must precede any read or

write packets (Figure 26). Transitions in the frame cali-

brate the oscillators on the MAX9257/MAX9258. The

baud rate of the synchronization frame sets the operat-

ing baud rate of the control channel. At power-up,

UART data rate must be between 95kbps to 400kbps.

After power-up, UART data rate can be programmed

according to Tables 28 and 29. Data is serialized start-

ing with the LSB first. The synchronization frame is 0x54

as shown in Figure 27.

Write Packet

The ECU writes the sync frame, 7-bit device address

plus read/write bit (R/

W = 0 for write), 8-bit register

address, number of bytes to be written, and data bytes

(Figure 28). The ECU must follow this UART protocol to

correctly program the MAX9257/MAX9258.

MAX9257/MAX9258

______________________________________________________________________________________

35

Fully Programmable Serializer/Deserializer

with UART/I

2

C Control Channel

I

2

C

REG ADDR

DATA 0

DATA N

LSB

MSB LSB

MSB

LSB

MSB

MAX9257

PERIPHERAL

ECU

MAX9258

UART

MSB

S

SLAVE ADDRESS

I

2

C SLAVE ADDRESS + Wr

W

A

REG ADDRESS

A

DATA 0

A

DATA N

A

LSB

MSB

LSB

MSB

LSB

P

Figure 25. UART-to-I

2

C Conversion

START

D3

D4

D5

D6

D7

PARITY

STOP

D0

D1

D2

Figure 26. UART Frame Format

1

0

1

0

1

0

0

0

START

SYNCHRONIZATION FRAME

STOP

PARITY

4

5

0

1

1

Figure 27. UART Synchronization Frame

NUMBER OF BYTES

REG ADDRESS

DEV ADDR +

R/W

SYNC

BYTE 1

BYTE N

Figure 28. UART Write Packet to MAX9257/MAX9258