Rainbow Electronics MAX9395 User Manual

General description, Applications, Features

General Description

The MAX9394/MAX9395 consist of a 2:1 multiplexer

and a 1:2 demultiplexer with loopback. The multiplexer

section (channel B) accepts two low-voltage differential

signaling (LVDS) inputs and generates a single LVDS

output. The demultiplexer section (channel A) accepts

a single LVDS input and generates two parallel LVDS

outputs. The MAX9394/MAX9395 feature a loopback

mode that connects the input of channel A to the output

of channel B and connects the selected input of chan-

nel B to the outputs of channel A.

Three LVCMOS/LVTTL logic inputs control the internal

connections between inputs and outputs, one for the

multiplexer portion of channel B (BSEL), and the other

two for loopback control of channels A and B (LB_SELA

and LB_SELB). Independent enable inputs for each dif-

ferential output pair provide additional flexibility.

Fail-safe circuitry forces the outputs to a differential low

condition for undriven inputs or when the common-

mode voltage exceeds the specified range. The

MAX9394 provides high-level input fail-safe detection

for HSTL, LVDS, and other GND-referenced differential

inputs. The MAX9395 provides low-level fail-safe detec-

tion for CML, LVPECL, and other V

CC

-referenced differ-

ential inputs.

Ultra low 91ps

P-P

(max) pseudorandom bit sequence

(PRBS) jitter ensures reliable communications in high-

speed links that are highly sensitive to timing error,

especially those incorporating clock-and-data recovery,

or serializers and deserializers. The high-speed switch-

ing performance guarantees 1.5GHz operation and less

than 87ps (max) skew between channels.

LVDS inputs and outputs are compatible with the

TIA/EIA-644 LVDS standard. The LVDS outputs drive

100

Ω loads. The MAX9394/MAX9395 are offered in 32-

pin TQFP and 28-pin thin QFN packages and operate

over the extended temperature range (-40°C to +85°C).

Applications

High-Speed Telecom/Datacom Equipment

Central Office Backplane Clock Distribution

DSLAM

Protection Switching

Fault-Tolerant Systems

Features

♦ Guaranteed 1.5GHz Operation with 250mV

Differential Output Swing

♦ Simultaneous Loopback Control

♦ 2ps

(RMS)

(max) Random Jitter

♦ AC Specifications Guaranteed for 150mV

Differential Input

♦ Signal Inputs Accept Any Differential Signaling

Standard

♦ LVDS Outputs for Clock or High-Speed Data

♦ High-Level Input Fail-Safe Detection (MAX9394)

♦ Low-Level Input Fail-Safe Detection (MAX9395)

♦ +3.0V to +3.6V Supply Voltage Range

♦ LVCMOS/LVTTL Logic Inputs

MAX9394/MAX9395

2:1 Multiplexers and 1:2 Demultiplexers with

Loopback

________________________________________________________________ Maxim Integrated Products

1

Ordering Information

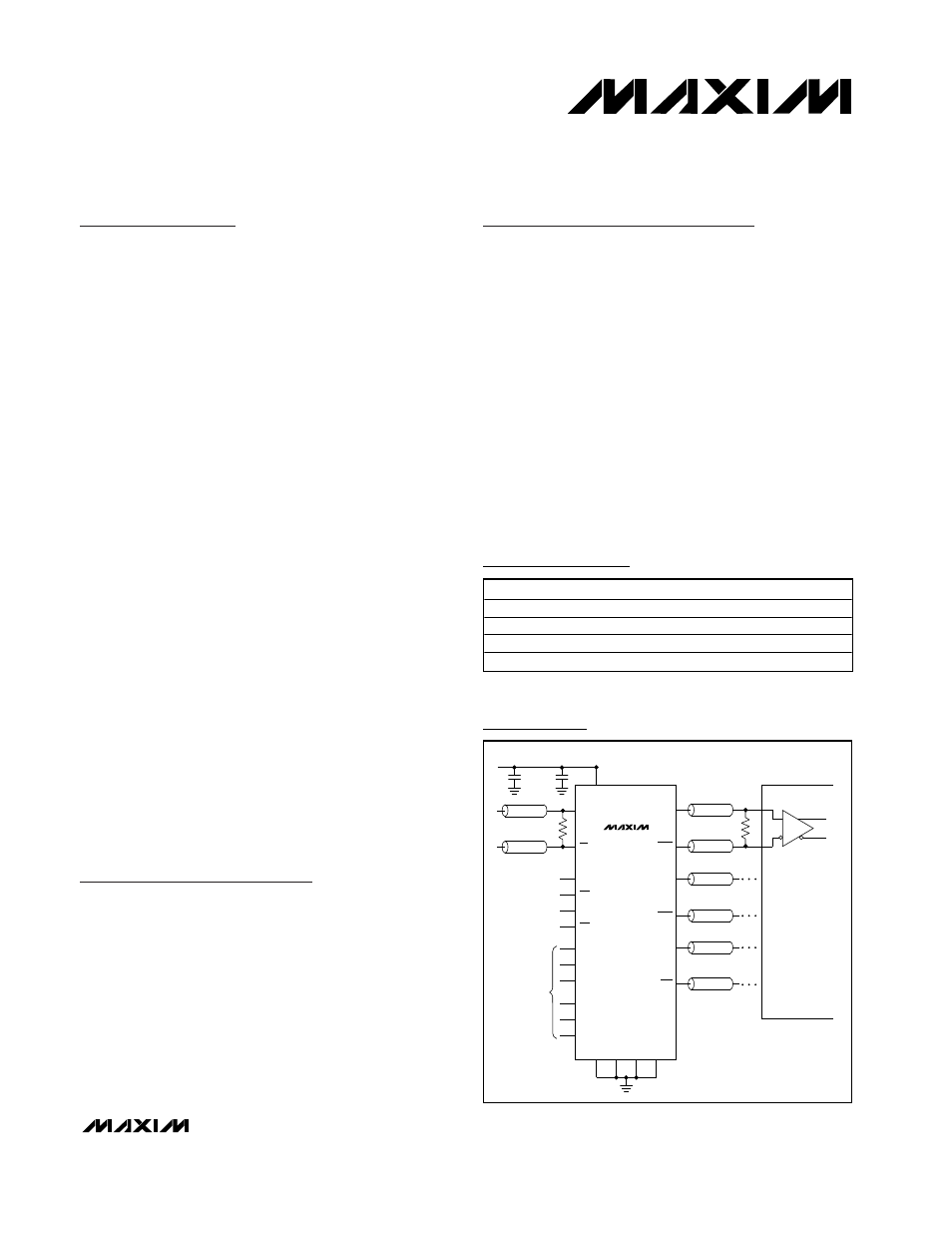

0.1

µF

0.01

µF

+3.0V TO

+3.6V

OUTA0

OUTA0

LVDS

RECEIVER

INA

INA

ENA0

ENA1

ENB

GND

GND

GND

GND

OUTA1

OUTA1

OUTB

OUTB

LVCMOS/LVTTL

LOGIC INPUTS

LB_SELA

LB_SELB

BSEL

INB0

INB0

100

Ω

Z

0

= 50

Ω

Z

0

= 50

Ω

MAX9394

MAX9395

V

CC

INB1

INB1

Z

0

= 50

Ω

Z

0

= 50

Ω

100

Ω

Z

0

= 50

Ω

Z

0

= 50

Ω

Z

0

= 50

Ω

Z

0

= 50

Ω

Typical Operating Circuit

19-2878; Rev 0; 7/03

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at

1-888-629-4642, or visit Maxim’s website at www.maxim-ic.com.

PART

TEMP RANGE

PIN-PACKAGE

MAX9394EHJ

-40°C to +85°C

32 TQFP

MAX9394ETI*

-40°C to +85°C

28 Thin QFN

MAX9395EHJ

-40°C to +85°C

32 TQFP

MAX9395ETI*

-40°C to +85°C

28 Thin QFN

*Future product—contact factory for availability.

Pin Configurations and Functional Diagram appear at end

of data sheet.