Rainbow Electronics SCAN92LV090 User Manual

General description, Features, Simplified functional diagram

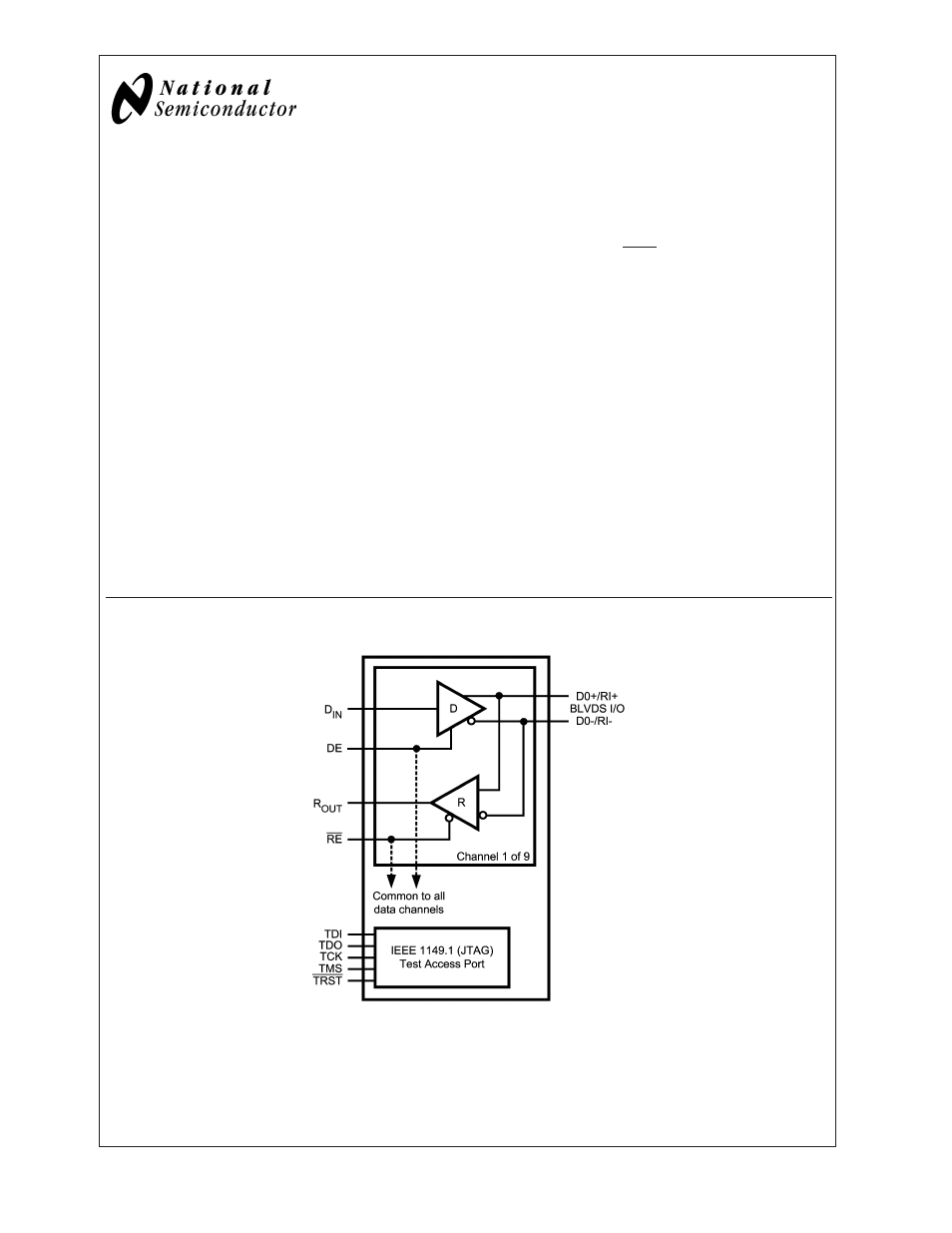

SCAN92LV090

9 Channel Bus LVDS Transceiver w/ Boundary SCAN

General Description

The SCAN92LV090A is one in a series of Bus LVDS trans-

ceivers designed specifically for the high speed, low power

proprietary backplane or cable interfaces. The device oper-

ates from a single 3.3V power supply and includes nine

differential line drivers and nine receivers. To minimize bus

loading, the driver outputs and receiver inputs are internally

connected. The separate I/O of the logic side allows for loop

back support. The device also features a flow through pin out

which allows easy PCB routing for short stubs between its

pins and the connector.

The driver translates 3V TTL levels (single-ended) to differ-

ential Bus LVDS (BLVDS) output levels. This allows for high

speed operation, while consuming minimal power with re-

duced EMI. In addition, the differential signaling provides

common mode noise rejection of

±

1V.

The receiver threshold is less than

±

100 mV over a

±

1V

common mode range and translates the differential Bus

LVDS to standard (TTL/CMOS) levels.

This device is compliant with IEEE 1149.1 Standard Test

Access Port and Boundary Scan Architecture with the incor-

poration of the defined boundary-scan test logic and test

access port consisting of Test Data Input (TDI), Test Data

Out (TDO), Test Mode Select (TMS), Test Clock (TCK), and

the optional Test Reset (TRST).

Features

n

IEEE 1149.1 (JTAG) Compliant

n

Bus LVDS Signaling

n

Low power CMOS design

n

High Signaling Rate Capability (above 100 Mbps)

n

0.1V to 2.3V Common Mode Range for V

ID

= 200mV

n

±

100 mV Receiver Sensitivity

n

Supports open and terminated failsafe on port pins

n

3.3V operation

n

Glitch free power up/down (Driver & Receiver disabled)

n

Light Bus Loading (5 pF typical) per Bus LVDS load

n

Designed for Double Termination Applications

n

Balanced Output Impedance

n

Product offered in 64 pin LQFP package and BGA

package

n

High impedance Bus pins on power off (V

CC

= 0V)

Simplified Functional Diagram

10124201

TRI-STATE

®

is a registered trademark of National Semiconductor Corporation.

February 2005

SCAN92L

V090

9

Channel

Bus

L

VDS

T

ransceiver

w/

Boundary

SCAN

© 2005 National Semiconductor Corporation

DS101242

www.national.com

Document Outline

- SCAN92LV090

- General Description

- Features

- Simplified Functional Diagram

- Connection Diagrams

- Pinout Description

- Absolute Maximum Ratings

- Recommended Operating Conditions

- DC Electrical Characteristics

- AC Electrical Characteristics

- Applications Information

- Test Circuits and Timing Waveforms

- FIGURE 1. Differential Driver DC Test Circuit

- FIGURE 2. Differential Driver Propagation Delay and Transition Time Test Circuit

- FIGURE 3. Differential Driver Propagation Delay and Transition Time Waveforms

- FIGURE 4. Driver TRI-STATE Delay Test Circuit

- FIGURE 5. Driver TRI-STATE Delay Waveforms

- FIGURE 6. Receiver Propagation Delay and Transition Time Test Circuit

- FIGURE 7. Receiver Propagation Delay and Transition Time Waveforms

- FIGURE 8. Receiver TRI-STATE Delay Test Circuit

- FIGURE 9. Receiver TRI-STATE Delay Waveforms

- Typical Bus Application Configurations

- Description of Boundary-Scan Circuitry

- Physical Dimensions