C control channel, Table 26. cto counter timeout period – Rainbow Electronics MAX9258 User Manual

Page 30

MAX9257/MAX9258

After the control channel closes, there is a brief hand-

shake period (T3 in Figure 22 and T5 in Figure 23)

between the MAX9257 and the MAX9258. The

MAX9258 sends a special lock frame to the MAX9257

to indicate if PLL is still locked. The MAX9258 sends the

lock frame if the number of decoding errors didn’t

exceed a threshold in the last LVDS video phase ses-

sion. The MAX9258 features a proprietary VCO lock

that prevents frequency drift while in the control chan-

nel for extended periods of time. If MAX9257 receives

the lock frame, it understands that the MAX9258 is in a

locked state and sends a short training sequence. If the

lock frame is not received by the MAX9257, it assumes

that the MAX9258 is not locked and sends a long train-

ing sequence. After the short or long training sequence

is complete, the MAX9257 sends three special synchro-

nization words before entering the video phase.

Training sequence is used to resynchronize the

MAX9257/MAX9258 before the video phase starts.

The MAX9257/MAX9258 control channel duration is

independent of VSYNC. The control channel does not

close when VSYNC deasserts, which allows the use of

a VSYNC interrupt signal on VSYNC_IN. The control

channel must be closed by STO, ETO, or EF. If the con-

trol channel does not close before video data becomes

available, video data can be lost.

STO/ETO Timer Programming

STO and ETO can be programmed given the values of

T2, T4, and maximum values of T1, T3, and T5 (Figures

22, 23):

t

T

= pixel clock period, t

UCLK

= UART period

When spread spectrum is not enabled in MAX9257:

max(T1) = 2.5µs + (3 x t

T

) + (4 x t

UCLK

)

When spread spectrum is enabled in MAX9257:

max(T1) = 2.5µs + (1400 x t

T

) + (4 x t

UCLK

)

T2 = t

STO

T4 = t

ETO

When pixel clock frequency range (PRATE) is 00 or 01:

When pixel clock frequency range (PRATE) is 10 or 11:

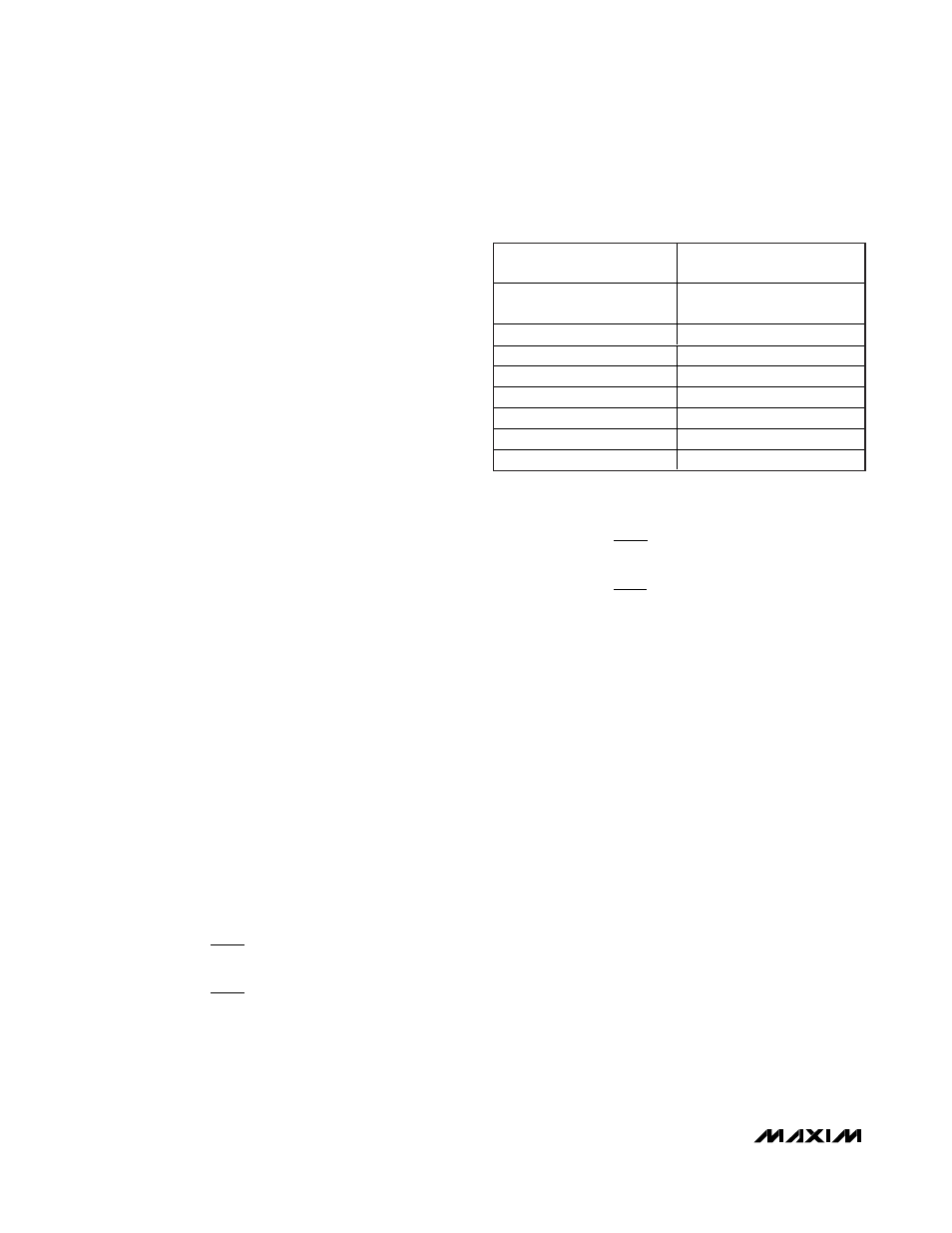

CTO Timer

The CTO (come-back timeout) timer temporarily or per-

manently blocks programming to the MAX9257/

MAX9258 registers. CTO keeps the MAX9257/ MAX9258

in bypass mode for the CTO timeout period (Table 26).

Bypass mode can only be exited when the CTO timer

expires. The CTO timer uses the UART bit times for its

counter. Note that STO and ETO timers use the pixel

clock while CTO uses the UART bit times. The UART

period t

UCLK

synchronizes with the UART bit times,

which synchronize every time the SYNC frame is sent.

When the CTO timer times out, INTEN bit in both

devices is set to 0 and the MAX9257/MAX9258 revert

back to base mode. If communication with the

MAX9257/MAX9258 is not needed after initial program-

ming is complete, CTO may be set to 000 (never come

back). In this case, CTO never expires and the

MAX9257/MAX9258 stay in bypass mode until they are

powered down. This prevents accidental programming

of the MAX9257/MAX9258 while ECU communicates

with the peripheral using a different UART protocol from

the MAX9257/MAX9258 UART protocol.

The overall CTO timeout is calculated as follows:

t

CTO

= t

UCLK

x CTO

max(

)

) (

)

max(

)

) (

)

T

t

t

t

T

t

t

t

STO

T

UCLK

ETO

T

UCLK

3

8

1090

20

5

8

1090

20

= ⎛

⎝⎜

⎞

⎠⎟

+

⎛

⎝⎜

⎞

⎠⎟

Ч

+

Ч

= ⎛

⎝⎜

⎞

⎠⎟

+

⎛

⎝⎜

⎞

⎠⎟

Ч

+

Ч

max(

)

) (

)

max(

)

) (

)

T

t

t

t

T

t

t

t

STO

T

UCLK

ETO

T

UCLK

3

8

546

20

5

8

546

20

= ⎛

⎝⎜

⎞

⎠⎟

+

⎛

⎝⎜

⎞

⎠⎟

Ч

+

Ч

= ⎛

⎝⎜

⎞

⎠⎟

+

⎛

⎝⎜

⎞

⎠⎟

Ч

+

Ч

30

______________________________________________________________________________________

Fully Programmable Serializer/Deserializer

with UART/I

2

C Control Channel

MAX9257 REG2[7:4]

MAX9258 REG3[7:4]

COUNTER USING UART BIT

TIMES

000

Never come back

(lockout)

001

16

010

32

011

48

100

64

101

80

110

96

111

112

Table 26. CTO Counter Timeout Period