C control channel – Rainbow Electronics MAX9258 User Manual

Page 25

tracks and passes the spread to the data and clock out-

puts. The PRATE range of 00 and 01 (5MHz ≤ PCLK ≤

20MHz) supports all the spread options. The PRATE

range of 10 and 11 (20MHz ≤ PCLK ≤ 70MHz) requires

that the spread be 2% or less.

Pixel Clock Jitter Filter

The MAX9257 has a PLL to filter high-frequency pixel

clock jitter on PCLK_IN. The FPLL can be bypassed by

writing 1 to REG4[2]. The FPLL improves the

MAX9258’s data recovery by filtering out the high-fre-

quency components from the pixel clock that the

MAX9258 cannot track. The 3db bandwidth of the FPLL

is 100kHz (typ).

LVDS Output Preemphasis (SDO±)

The MAX9257 features programmable preemphasis

where extra current is added when the LVDS outputs

transition on the serial link. Preemphasis provides addi-

tional current to the normal drive current. For example,

20% preemphasis provides 20% greater current than

the normal drive current. Current is boosted only on the

transitions and returns to the normal drive current after

switching. Select the preemphasis level to optimize the

eye diagram. Preemphasis boosts the high-frequency

content of the LVDS outputs to enable driving greater

cable lengths. The amount of preemphasis is pro-

grammed in REG12[7:5] (Table 21).

VSYNC, HSYNC, and Pixel Clock Polarity

PCLK: The MAX9257 is programmable to latch data on

either rising or falling edge of PCLK. The polarity of

PCLKOUT at the MAX9258 can be independent of the

MAX9257 PCLK active edge. The polarity of PCLK can

be programmed using REG4[5] of the MAX9257 and

the MAX9258.

VSYNC: The MAX9257 and the MAX9258 enter control

channel on the falling edge of VSYNC. The default reg-

ister settings are VSYNC active falling edge for both the

MAX9257 and the MAX9258. If the VSYNC active edge

is programmed for rising edge at the MAX9257, the

MAX9258 VSYNC active edge must also be pro-

grammed for rising edge to reproduce VSYNC rising

edge at the MAX9258 output. However, matching the

polarity of the VSYNC active edge between the

MAX9257 and the MAX9258 is not a requirement for

proper operation.

HSYNC: HSYNC active-edge polarity is programmable

for the MAX9258.

General Purpose I/Os (GPIOs)

The MAX9257 has up to 10 GPIOs available. GPIO8

and GPIO9 are always available while GPIO[0:7] are

available depending on the parallel-word width (Table

22). If GPIOs are not available, the corresponding GPIO

bits are not used.

MAX9257/MAX9258

______________________________________________________________________________________

25

Fully Programmable Serializer/Deserializer

with UART/I

2

C Control Channel

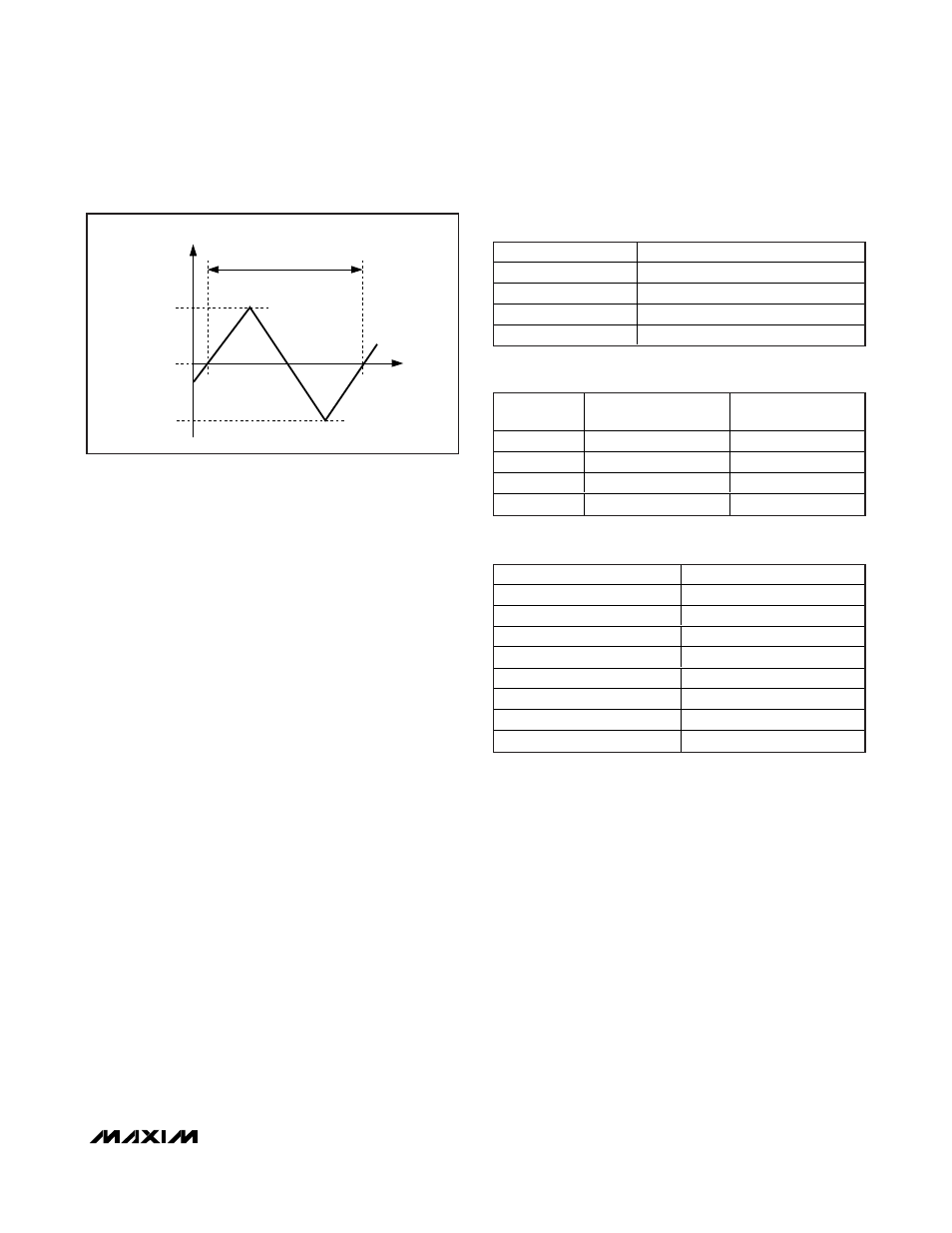

FREQUENCY

TIME

f

SPREAD

(MAX)

f

PCLK_IN

f

SPREAD

(MIN)

1/f

SSM

Figure 21. Simplified Modulation Profile for the MAX9257/MAX9258

PRATE (REG1[7:6])

SPREAD (%)

00

Off

01

±2

10

Off

11

±4

Table 17. MAX9258 Spread

PRATE

(REG1[7:6])

MODULATION RATE

f

SSM

RANGE (kHz)

00

PCLK/312

16 to 32

01

PCLK/520

19.2 to 38.5

10

PCLK/1040

19.2 to 38.5

11

PCLK/1248

32 to 56

Table 18. MAX9258 Modulation Rate

REG1[7:5]

SPREAD (%)

000

Off

001

±1.5

010

±1.75

011

±2

100

Off

101

±3

110

±3.5

111

±4

Table 19. MAX9257 LVDS Output Spread