Texas Instruments Digital Signal Processor SM320F2812-HT User Manual

Page 70

SGUS062B

–

JUNE 2009

–

REVISED JUNE 2011

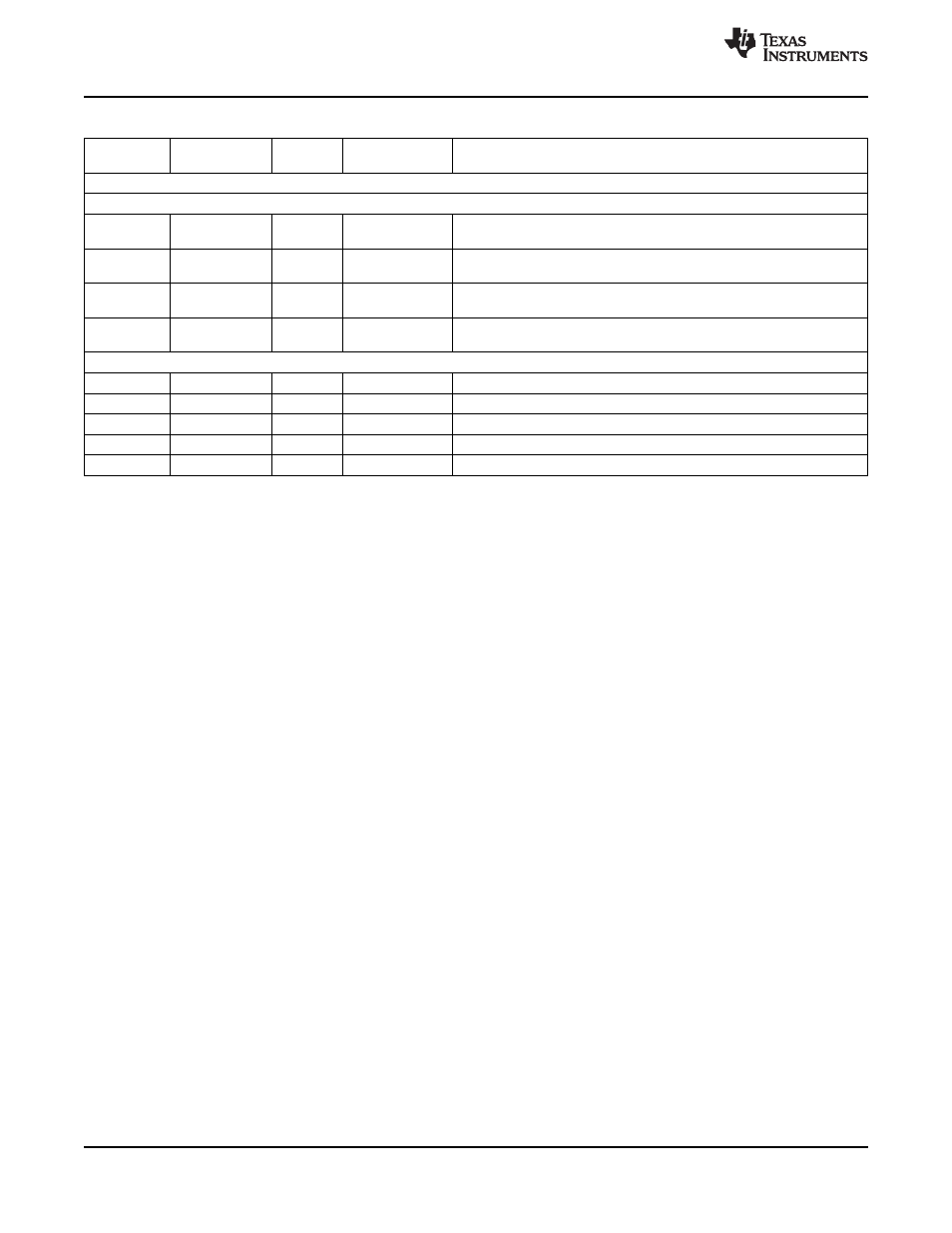

Table 4-7. McBSP Register Summary (continued)

ADDRESS

TYPE

RESET VALUE

NAME

DESCRIPTION

0x00 78xxh

(R/W)

(HEX)

FIFO MODE REGISTERS (applicable only in FIFO mode)

FIFO Data Registers

(1)

McBSP Data Receive Register 2

–

Top of receive FIFO

DRR2

00

R

0x0000

–

Read First FIFO pointers does not advance

McBSP Data Receive Register 1

–

Top of receive FIFO

DRR1

01

R

0x0000

–

Read Second for FIFO pointers to advance

McBSP Data Transmit Register 2

–

Top of transmit FIFO

DXR2

02

W

0x0000

–

Write First FIFO pointers does not advance

McBSP Data Transmit Register 1

–

Top of transmit FIFO

DXR1

03

W

0x0000

–

Write Second for FIFO pointers to advance

FIFO Control Registers

MFFTX

20

R/W

0xA000

McBSP Transmit FIFO Register

MFFRX

21

R/W

0x201F

McBSP Receive FIFO Register

MFFCT

22

R/W

0x0000

McBSP FIFO Control Register

MFFINT

23

R/W

0x0000

McBSP FIFO Interrupt Register

MFFST

24

R/W

0x0000

McBSP FIFO Status Register

(1)

FIFO pointers advancing is based on order of access to DRR2/DRR1 and DXR2/DXR1 registers.

70

Peripherals

Copyright

©

2009

–

2011, Texas Instruments Incorporated

Product Folder Link(s):