4 peripherals, 1 32-bit cpu-timers 0/1/2, 4peripherals – Texas Instruments Digital Signal Processor SM320F2812-HT User Manual

Page 50

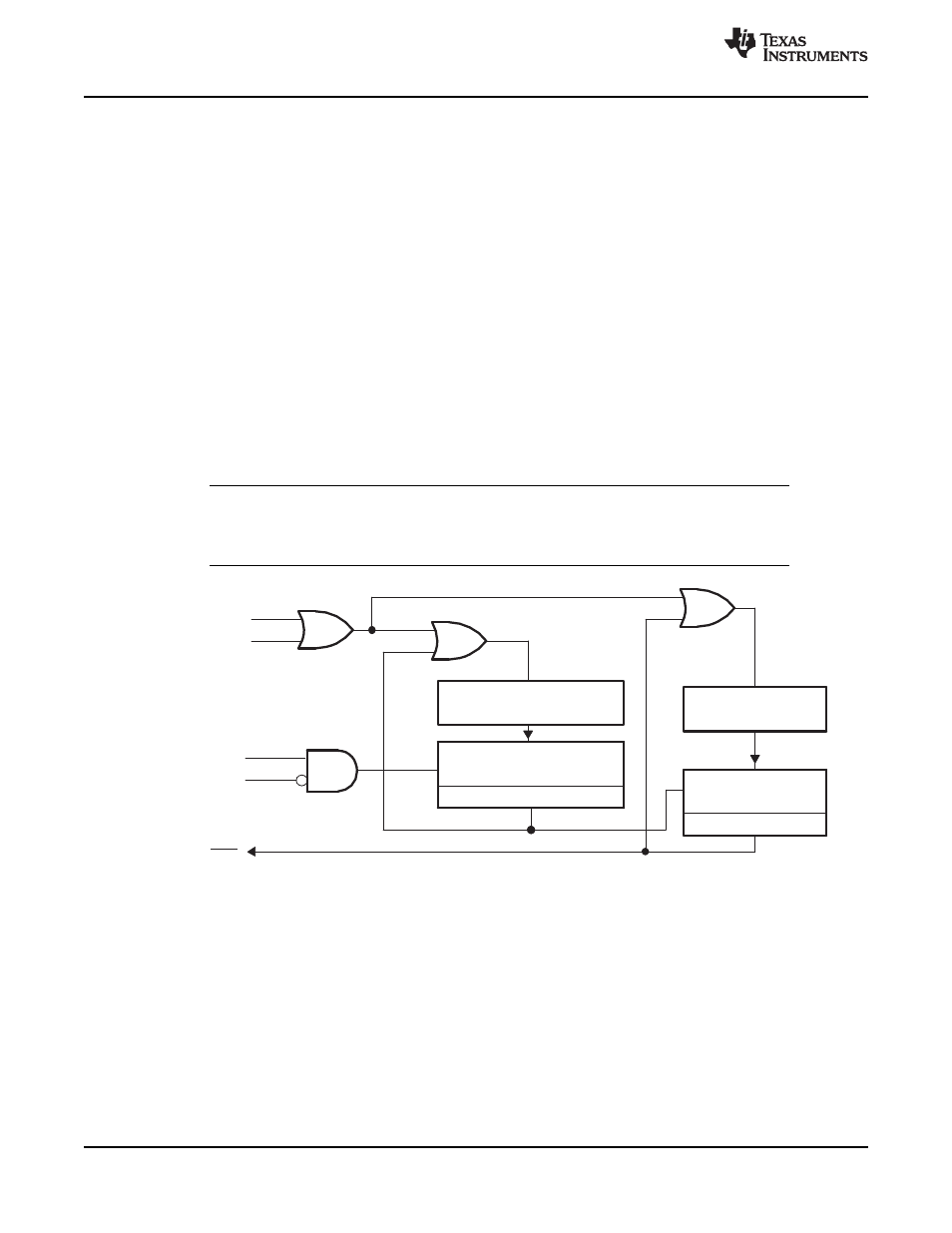

Borrow

Reset

Timer Reload

SYSCLKOUT

TCR.4

(Timer Start Status)

TINT

16-Bit Timer Divide-Down

TDDRH:TDDR

32-Bit Timer Period

PRDH:PRD

32-Bit Counter

TIMH:TIM

16-Bit Prescale Counter

PSCH:PSC

Borrow

SGUS062B

–

JUNE 2009

–

REVISED JUNE 2011

4

Peripherals

The integrated peripherals of the F2812 are described in the following subsections:

•

Three 32-bit CPU-Timers

•

Two event-manager modules (EVA, EVB)

•

Enhanced analog-to-digital converter (ADC) module

•

Enhanced controller area network (eCAN) module

•

Multichannel buffered serial port (McBSP) module

•

Serial communications interface modules (SCI-A, SCI-B)

•

Serial peripheral interface (SPI) module

•

Digital I/O and shared pin functions

4.1

32-Bit CPU-Timers 0/1/2

There are three 32-bit CPU-timers on the F2812 devices (CPU-TIMER0/1/2).

CPU-Timers 1 and 2 are reserved for the real-time OS (such as DSP/BIOS). CPU-Timer 0 can be used in

user applications. These timers are different from the general-purpose (GP) timers that are present in the

Event Manager modules (EVA, EVB).

NOTE

If the application is not using DSP/BIOS, then CPU-Timers 1 and 2 can be used in the

application.

Figure 4-1. CPU-Timers

50

Peripherals

Copyright

©

2009

–

2011, Texas Instruments Incorporated

Product Folder Link(s):