Texas Instruments Digital Signal Processor SM320F2812-HT User Manual

Page 64

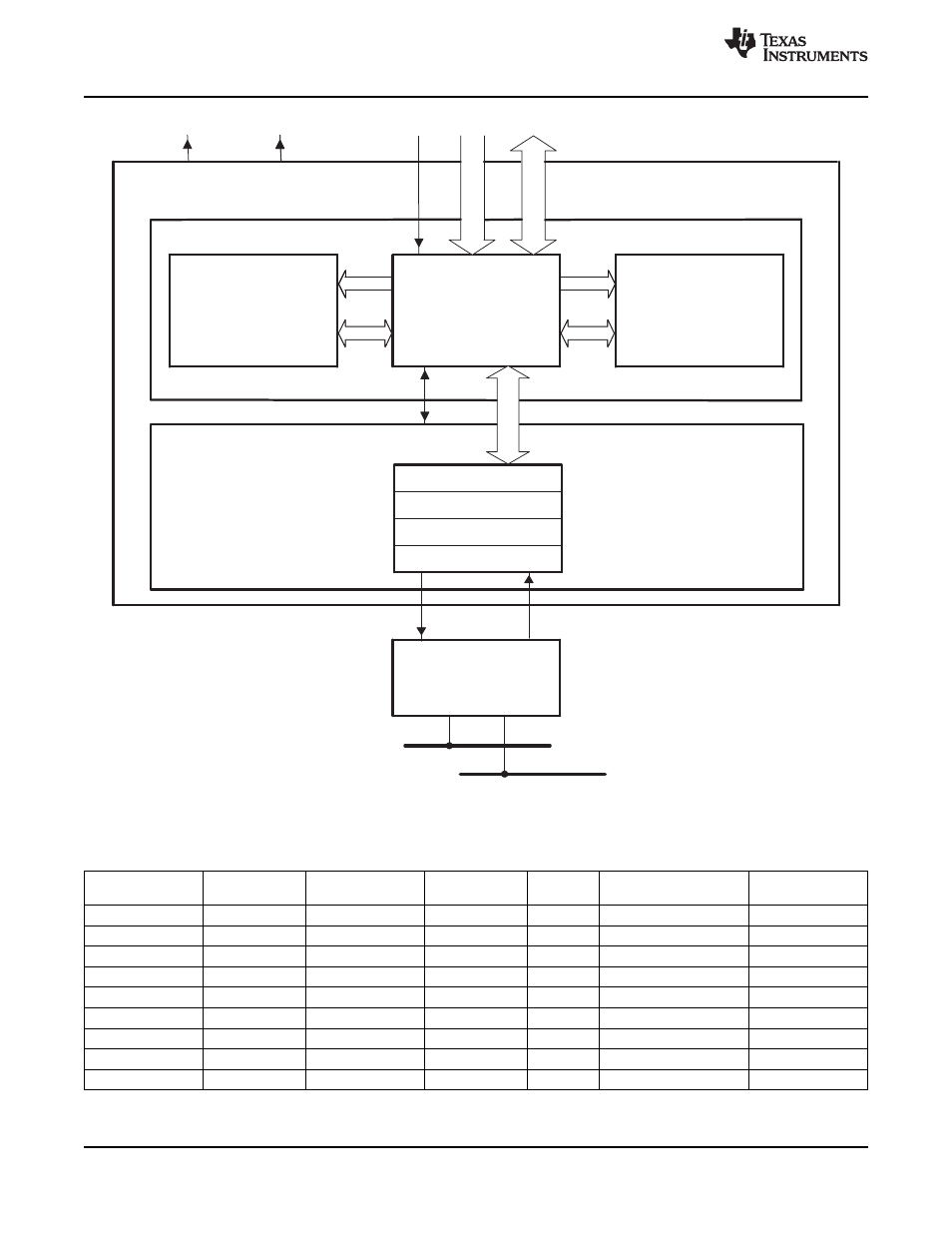

Mailbox RAM

(512 Bytes)

32-Message Mailbox

of 4

×

32-Bit Words

Memory Management

Unit

CPU Interface,

Receive Control Unit,

Timer Management Unit

eCAN Memory

(512 Bytes)

Registers and Message

Objects Control

32

32

Message Controller

32

32

32

32

32

32

eCAN Protocol Kernel

Receive Buffer

Transmit Buffer

Control Buffer

Status Buffer

Enhanced CAN Controller

32

Controls

Address

Data

eCAN1INT

eCAN0INT

32

SN65HVD23x

3.3-V CAN Transceiver

CAN Bus

SGUS062B

–

JUNE 2009

–

REVISED JUNE 2011

Figure 4-7. eCAN Block Diagram and Interface Circuit

Table 4-5. 3.3-V eCAN Transceivers for the SM320F2812 DSP

SUPPLY

LOW-POWER

SLOPE

PART NUMBER

VREF

OTHER

T

A

VOLTAGE

MODE

CONTROL

SN65HVD230

3.3 V

Standby

Adjustable

Yes

–

–

40

°

C to 85

°

C

SN65HVD230Q

3.3 V

Standby

Adjustable

Yes

–

–

40

°

C to 125

°

C

SN65HVD231

3.3 V

Sleep

Adjustable

Yes

–

–

40

°

C to 85

°

C

SN65HVD231Q

3.3 V

Sleep

Adjustable

Yes

–

–

40

°

C to 125

°

C

SN65HVD232

3.3 V

None

None

None

–

–

40

°

C to 85

°

C

SN65HVD232Q

3.3 V

None

None

None

–

–

40

°

C to 125

°

C

SN65HVD233

3.3 V

Standby

Adjustable

None

Diagnostic Loopback

–

40

°

C to 125

°

C

SN65HVD234

3.3 V

Standby

&

Sleep

Adjustable

None

–

–

40

°

C to 125

°

C

SN65HVD235

3.3 V

Standby

Adjustable

None

Autobaud Loopback

–

40

°

C to 125

°

C

64

Peripherals

Copyright

©

2009

–

2011, Texas Instruments Incorporated

Product Folder Link(s):