Texas Instruments Digital Signal Processor SM320F2812-HT User Manual

Page 115

SGUS062B

–

JUNE 2009

–

REVISED JUNE 2011

LW

≥

t

c(XTIM)

These requirements result in the following XTIMING register configuration restrictions:

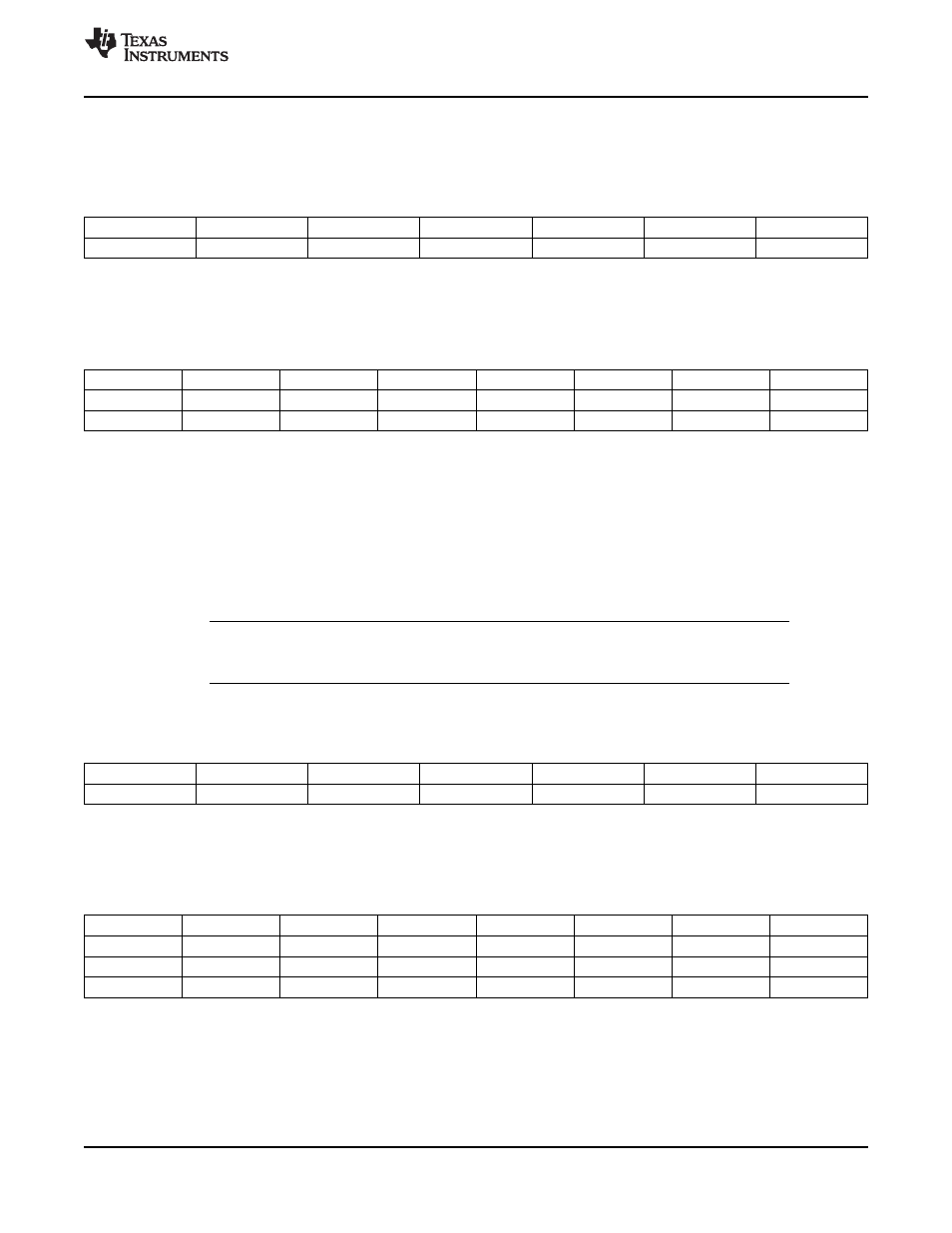

Table 6-26. XTIMING Register Configuration Restrictions

(1) (2)

XRDLEAD

XRDACTIVE

XRDTRAIL

XWRLEAD

XWRACTIVE

XWRTRAIL

X2TIMING

≥

1

≥

0

≥

0

≥

1

≥

0

≥

0

0, 1

(1)

Not production tested.

(2)

No hardware to detect illegal XTIMING configurations

Examples

of

valid

and

invalid

timing

when

not

sampling

XREADY:

Table 6-27. Valid and Invalid Timing

(1) (2)

XRDLEAD

XRDACTIVE

XRDTRAIL

XWRLEAD

XWRACTIVE

XWRTRAIL

X2TIMING

Invalid

0

0

0

0

0

0

0, 1

Valid

1

0

0

1

0

0

0, 1

(1)

Not production tested.

(2)

No hardware to detect illegal XTIMING configurations

•

If the XREADY signal is sampled in the Synchronous mode (USEREADY = 1, READYMODE = 0),

then:

1. Lead:

LR

≥

t

c(XTIM)

LW

≥

t

c(XTIM)

2. Active:

AR

≥

2

×

t

c(XTIM)

AW

≥

2

×

t

c(XTIM)

NOTE

Restriction does not include external hardware wait states

These requirements result in the following XTIMING register configuration restrictions:

Table 6-28. XTIMING Register Configuration Restrictions

(1) (2)

XRDLEAD

XRDACTIVE

XRDTRAIL

XWRLEAD

XWRACTIVE

XWRTRAIL

X2TIMING

≥

1

≥

1

≥

0

≥

1

≥

1

≥

0

0, 1

(1)

Not production tested.

(2)

No hardware to detect illegal XTIMING configurations

Examples of valid and invalid timing when using Synchronous XREADY:

Table 6-29. Valid and Invalid Timing when using Synchronous XREADY

(1) (2)

XRDLEAD

XRDACTIVE

XRDTRAIL

XWRLEAD

XWRACTIVE

XWRTRAIL

X2TIMING

Invalid

0

0

0

0

0

0

0, 1

Invalid

1

0

0

1

0

0

0, 1

Valid

1

1

0

1

1

0

0, 1

(1)

Not production tested.

(2)

No hardware to detect illegal XTIMING configurations

•

If the XREADY signal is sampled in the Asynchronous mode (USEREADY = 1, READYMODE = 1),

then:

1. Lead:

LR

≥

t

c(XTIM)

LW

≥

t

c(XTIM)

Copyright

©

2009

–

2011, Texas Instruments Incorporated

Electrical Specifications

115

Product Folder Link(s):