9 emac module, 1 emac module components – Texas Instruments TMS320TCI6486 User Manual

Page 52

Clock and

reset logic

Receive

DMA engine

Interrupt

controller

Transmit

DMA engine

Control

registers

EMIC

Receive

FIFO

MAC

receiver

State

RAM

Statistics

Transmit

FIFO

MAC

transmitter

Receive

address

SYNC

RMII0, RMII1

RGMII0, RGMII1

MII0/GMII0

S3MII0, S3MII1

Configuration bus

CPPI

buffer

manager

Configuration bus

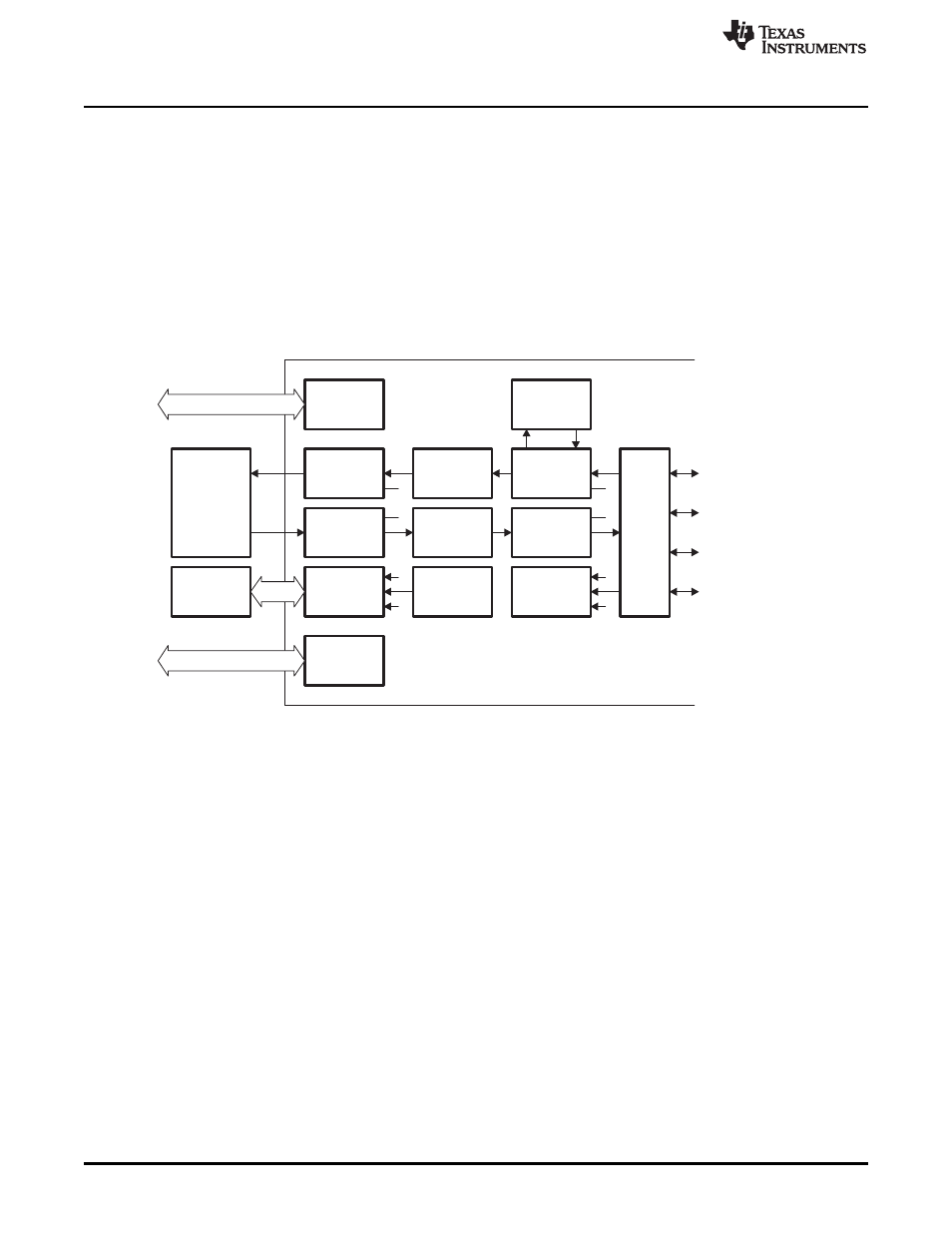

EMAC Functional Architecture

www.ti.com

2.9

EMAC Module

This section discusses the architecture and basic functions of the EMAC sub-module integrated with the

TCI6486/C6472 device.

2.9.1

EMAC Module Components

There are two EMAC modules integrated with the TCI6486/C6472 device. EMAC0 interfaces with PHY

through one of five interfaces: MII, GMII, S3MII, RMII, or RGMII. EMAC1 interfaces with PHY through one

of three interfaces: S3MII, RMII, or RGMII. In

, the number associated with each MII interface

shows the EMAC module with which the interface is available. For example: RMII0 is EMAC0 interface,

RMII1 is EMAC1 interface.

Figure 22. EMAC Module Block Diagram

Each EMAC peripheral used has the following components:

•

The receive path:

–

Receive DMA engine

The receive DMA engine performs the data transfer between the receive FIFO and the device

internal or external memory. It interfaces to the processor through the bus arbiter in the CPPI buffer

manager. This DMA engine is totally independent of the TCI6486/C6472 DSP EDMA.

–

Receive FIFO

The receive FIFO consists of 68 cells of 64 bytes each and the associated control logic. The FIFO

buffers receive data in preparation for writing into packet buffers in device memory and also enable

receive FIFO flow control.

–

MAC receiver

The MAC receiver detects and processes incoming network frames, de-frames them, and places

them into the receive FIFO. The MAC receiver also detects errors and passes statistics to the

statistics RAM.

–

Receive address sub-module

The receive address sub-module performs address matching and address filtering based on the

incoming packet's destination address. It contains a 32 x 53 bit two-port RAM in which up to 32

addresses can be stored to be either matched or filtered by the EMAC.

The RAM may contain multicast packet addresses, but the associated channel must have the

unicast enable bit set, even though it is a multicast address. The unicast enable bits are used with

multicast addresses in the receive address RAM (not the multicast hash enable bits). Therefore,

hash matches can be disabled, but specific multicast addresses can be matched (or filtered) in the

RAM. If a multicast packet hash matches, the packet may still be filtered in the RAM. Each packet

52

C6472/TCI6486 EMAC/MDIO

SPRUEF8F – March 2006 – Revised November 2010

Copyright © 2006–2010, Texas Instruments Incorporated