25 receive buffer offset register (rxbufferoffset), Section 5.25 – Texas Instruments TMS320TCI6486 User Manual

Page 121

www.ti.com

EMAC Port Registers

5.25 Receive Buffer Offset Register (RXBUFFEROFFSET)

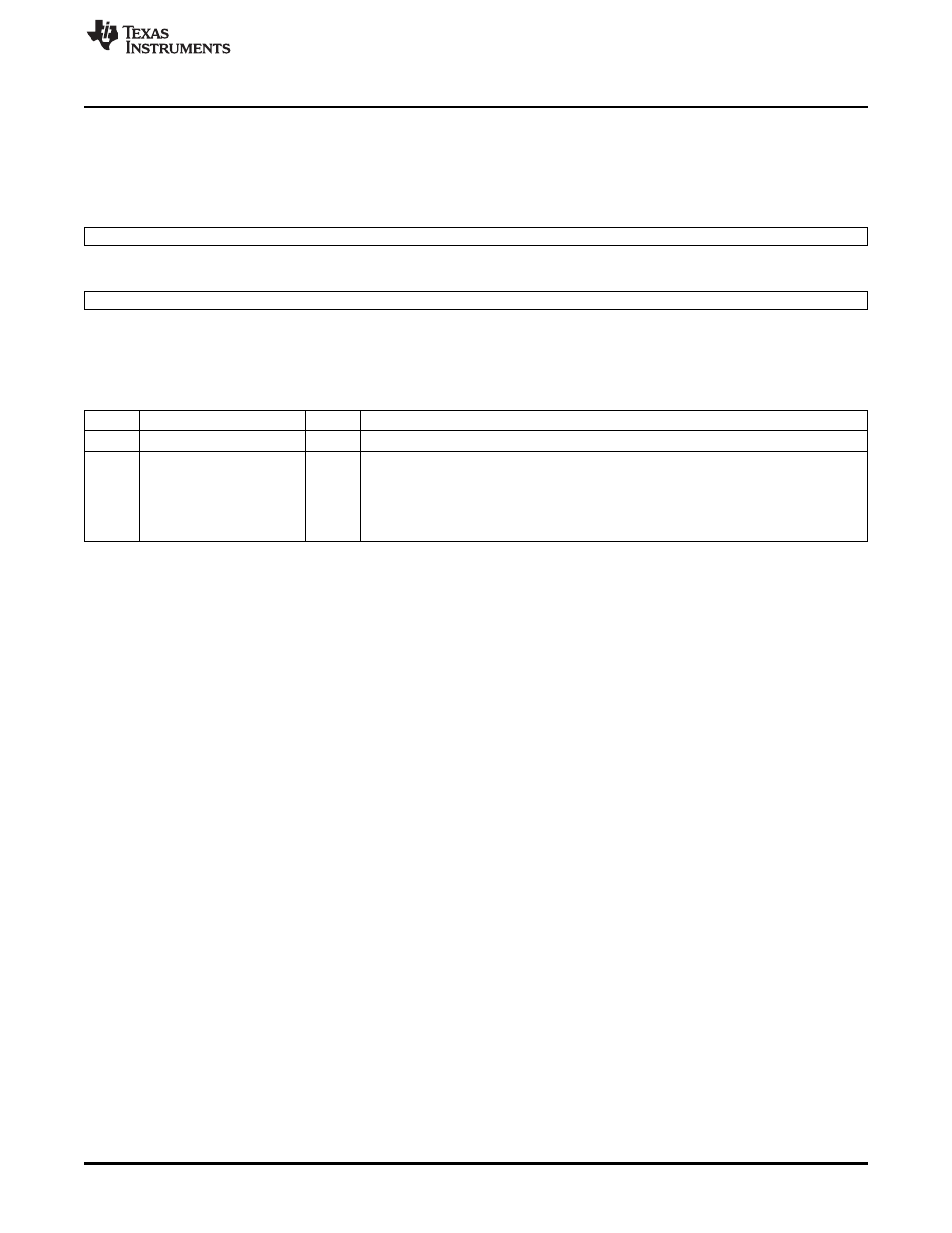

The receive buffer offset register (RXBUFFEROFFSET) is shown in

and described in

Figure 67. Receive Buffer Offset Register (RXBUFFEROFFSET)

31

16

Reserved

R-0

15

0

RXBUFFEROFFSET

R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 61. Receive Buffer Offset Register (RXBUFFEROFFSET) Field Descriptions

Bit

Field

Value

Description

31-16

Reserved

0

Reserved

15-0

RXBUFFEROFFSET

Receive buffer offset value. These bits are written by the EMAC into each frame SOP

buffer descriptor Buffer Offset field. The frame data begins after the RXBUFFEROFFSET

value of bytes. A value of 0 indicates that there are no unused bytes at the beginning of

the data and that valid data begins on the first byte of the buffer. A value of Fh (15)

indicates that the first 15 bytes of the buffer are to be ignored by the EMAC and that valid

buffer data starts on byte 16 of the buffer. This value is used for all channels.

121

SPRUEF8F – March 2006 – Revised November 2010

C6472/TCI6486 EMAC/MDIO

Copyright © 2006–2010, Texas Instruments Incorporated