Texas Instruments TMS320TCI6486 User Manual

Page 51

www.ti.com

EMAC Functional Architecture

The implementation of these macros using the register layer Chip Support Library (CSL) is shown in

(USERACCESS0 is assumed).

Note that this implementation does not check the ACK bit on PHY register reads; in other words, it does

not follow the procedure outlined in

. As the ALIVE register initially selects a PHY, it is

assumed that the PHY is acknowledging read operations. It is possible that a PHY could become inactive

at a future point in time. For example, a PHY can have its MDIO addresses changed while the system is

running, although it is not a common occurrence. This condition can be tested by periodically checking the

PHY state in the ALIVE register.

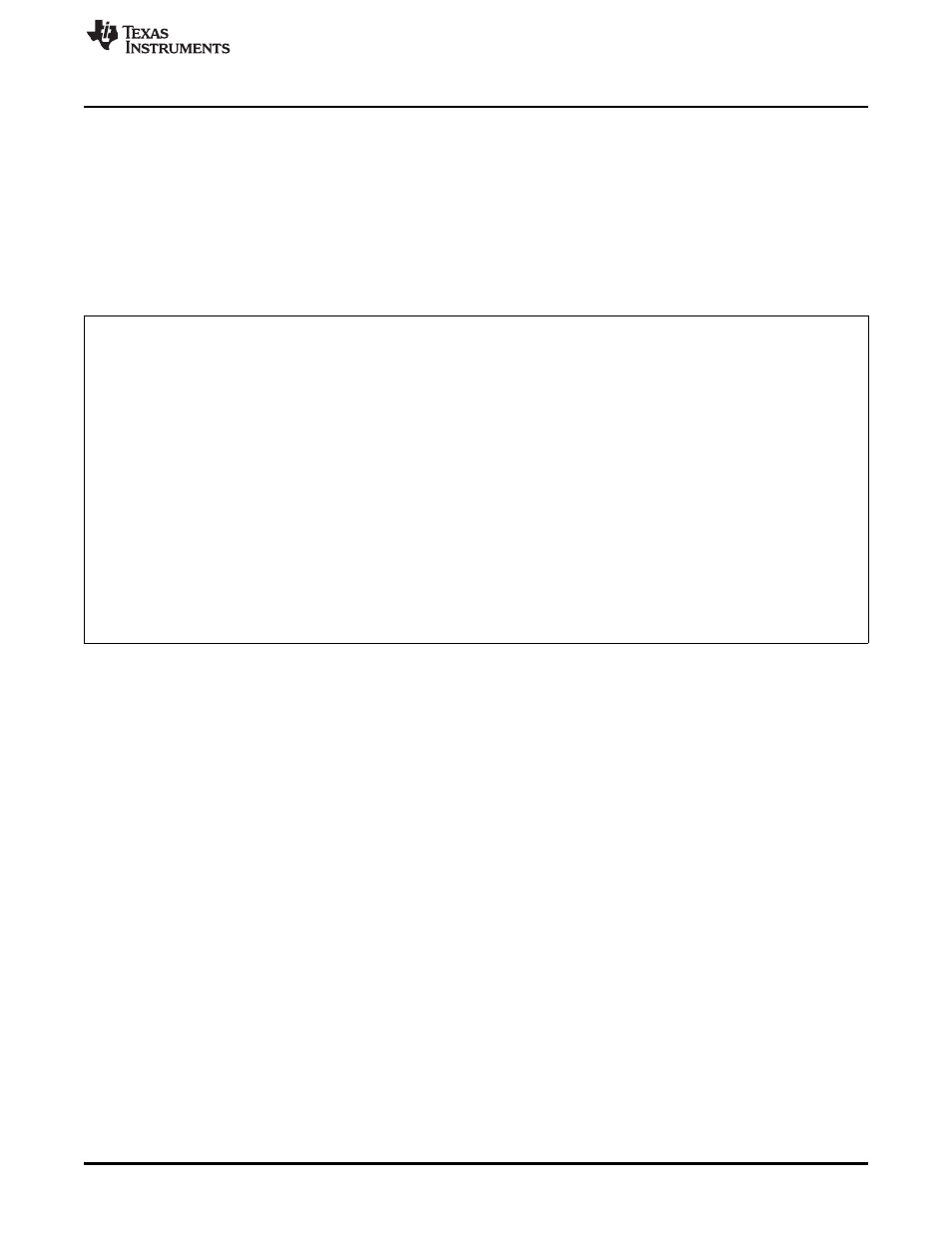

Example 3. MDIO Register Access Macros

#define PHYREG_read(regadr,

phyadr)

\

MDIO_REGS->USERACCESS0 =

\

CSL_FMK(MDIO_USERACCESS0_GO,1u)

|

\

CSL_FMK(MDIO_USERACCESS0_REGADR,regadr) |

\

CSL_FMK(MDIO_USERACCESS0_PHYADR,phyadr)

#define PHYREG_write(regadr,

phyadr,

data)

\

MDIO_REGS->USERACCESS0 =

\

CSL_FMK(MDIO_USERACCESS0_GO,1u)

|

\

CSL_FMK(MDIO_USERACCESS0_WRITE,1)

|

\

CSL_FMK(MDIO_USERACCESS0_REGADR,regadr) |

\

CSL_FMK(MDIO_USERACCESS0_PHYADR,phyadr) |

\

CSL_FMK(MDIO_USERACCESS0_DATA, data)

#define PHYREG_wait()

\

while (CSL_FEXT(MDIO_REGS->USERACCESS0,MDIO_USERACCESS0_GO) )

#define PHYREG_wait

Results(results

)

{

\

while (CSL_FEXT(MDIO_REGS->USERACCESS0,MDIO_USERACCESS0_GO) );

\

results = CSL_FEXT(MDIO_REGS->USERACCESS0, MDIO_USERACCESS0_DATA); }

51

SPRUEF8F – March 2006 – Revised November 2010

C6472/TCI6486 EMAC/MDIO

Copyright © 2006–2010, Texas Instruments Incorporated