2 timed delay state machine (tdsm) – Texas Instruments TMS320TCI6486 User Manual

Page 43

Waiting

Delay

Time=0

Time=0

Output

EVT

_PU

LSE=0

&&

D

IV

_N

EXT

=1

EVT_PULSE=1&&

TIME<

TIME_CFG

EVT_PULSE=1

&&

DIV_NEXT=1

PS_TICK=1 &&

TIME < TIME_CFG

&& DIV_NEXT=0

EVT_PULSE=1 &&

TIME < TIME_CFG

EVT_PULSE=0 (or)

EVT_PULSE=1 && TIME >= TIME_CFG

Increment

time

Time=0

PS_TICK=0 &&

DIV_NEXT=0

PS_TICK=1

&&

TIME

>= TIME_CFG

Time=0

Time=0

EVT_PULSE = 0 (or)

EVT_PULSE = 1 && TIME >= TIME_CFG

www.ti.com

EMAC Functional Architecture

2.7.2

Timed Delay State Machine (TDSM)

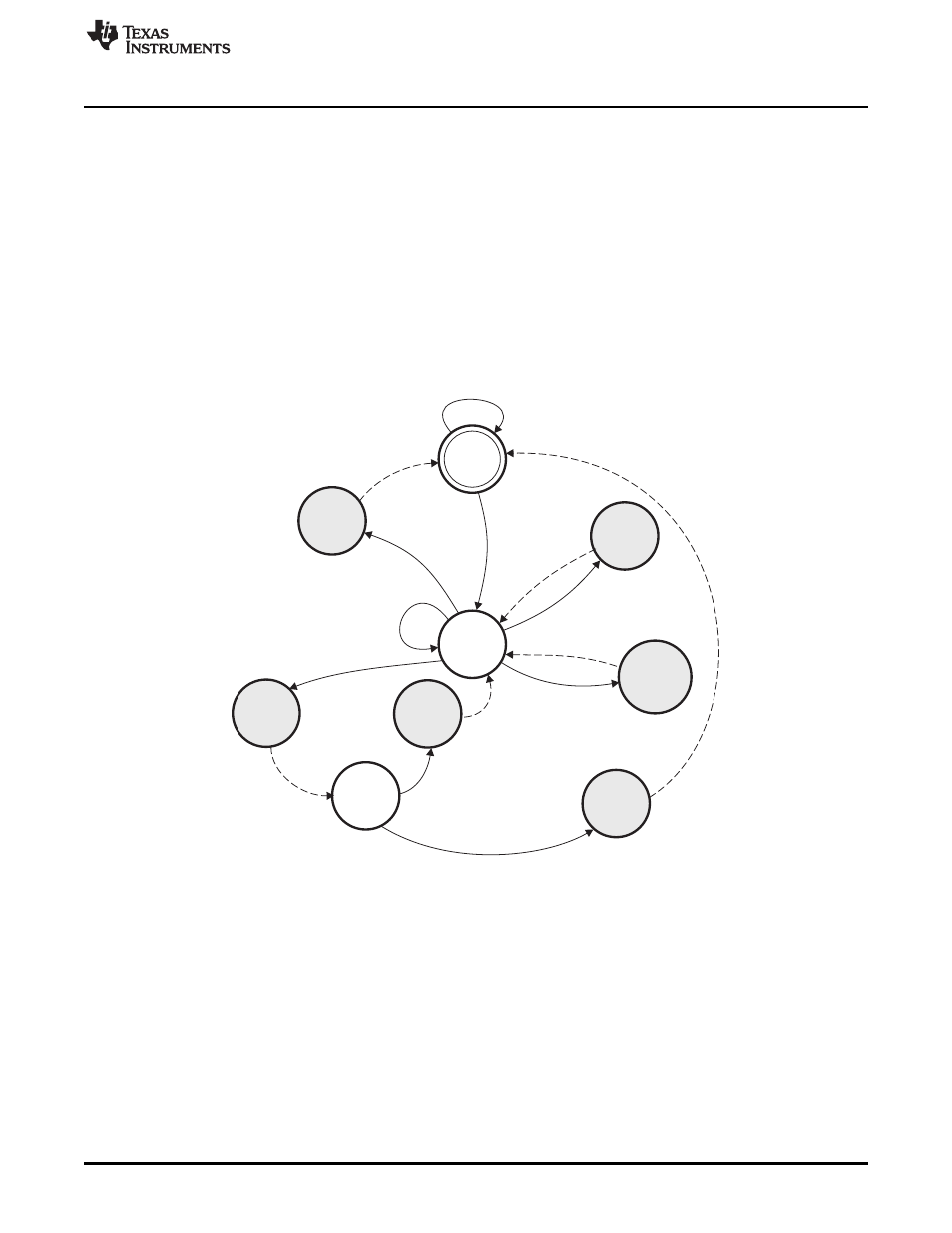

The timed-delay state machine fully implements the functionality of the time-delay based interrupt pacing.

The TIME_CFG bit field of the TPCFG and RPCFG registers (described in

) is set to 0 on reset

and disables this state machine. When the TIME_CFG is set to a non-zero value, an output pulse is

generated after the TIME_CFG number of prescalar output periods. The counter starts counting on the

first event.

The state machine has three states, WAITING, DELAY, and OUTPUT. Upon reset, the state machine is

placed in the WAITING state. The state machine makes transitions between the states as shown in

. Note that states that are grayed out are transitional states, in the sense that the SM does not

stay in the grayed state. While in the transitional state, it typically does an operation, like incrementing the

TIME or resetting the TIME. It then changes the state to the state illustrated by the dotted line.

Figure 16. TDSM State Transition Diagram

43

SPRUEF8F – March 2006 – Revised November 2010

C6472/TCI6486 EMAC/MDIO

Copyright © 2006–2010, Texas Instruments Incorporated