Texas Instruments MSP50C6xx User Manual

Page 95

Instruction Syntax and Addressing Modes

4-9

Assembly Language Instructions

4.3.2

Addressing Modes

The addressing modes on the MSP50P614/MSP50C614 are immediate, di-

rect, indirect with post modification, and three relative modes. The relative

modes are:

-

Relative to the INDEX or R5 register. The effective address is (indirect reg-

ister + INDEX).

-

Short relative to the PAGE or R6 register. The effective address is

(PAGE+7-bit positive offset).

-

Long relative to Rx. The effective address is (indirect register Rx + 16-bit

positive offset).

When string instructions are executed, the operation of the addressing mode

used is modified. For all addressing modes except indirect with post modifica-

tion, a temporary copy of the memory address is used to fetch the least signifi-

cant data word of the string. Over the next n instruction cycles, the temporary

copy of the address is auto-incremented to fetch the next n words of the string.

Since the modification of the address is temporary, all Rx registers are un-

changed and still have reference to the least significant data word in memory.

String data fetches using the indirect with post modification addressing mode

and writes the modified address back to the indirect register at each cycle of

the string. This will leave the address in the Rx register pointing to the data

word whose address is one beyond the most significant word of the string.

All addressing modes except immediate addressing are encoded in bits 0 to

7 of the instruction’s op-code. Table 4–2 through Table 4–6 show the encoding

of various addressing modes. Addressing mode bits (except immediate and

flag addressing) come with an am, Rx and pm field. These are combined into

a single field called {adrs}. The appropriate decoding and syntax for each ad-

dressing mode with the {adrs} field is described in Table 4–4. The pm field only

applies to indirect addressing. For other addressing modes, it is coded as zero.

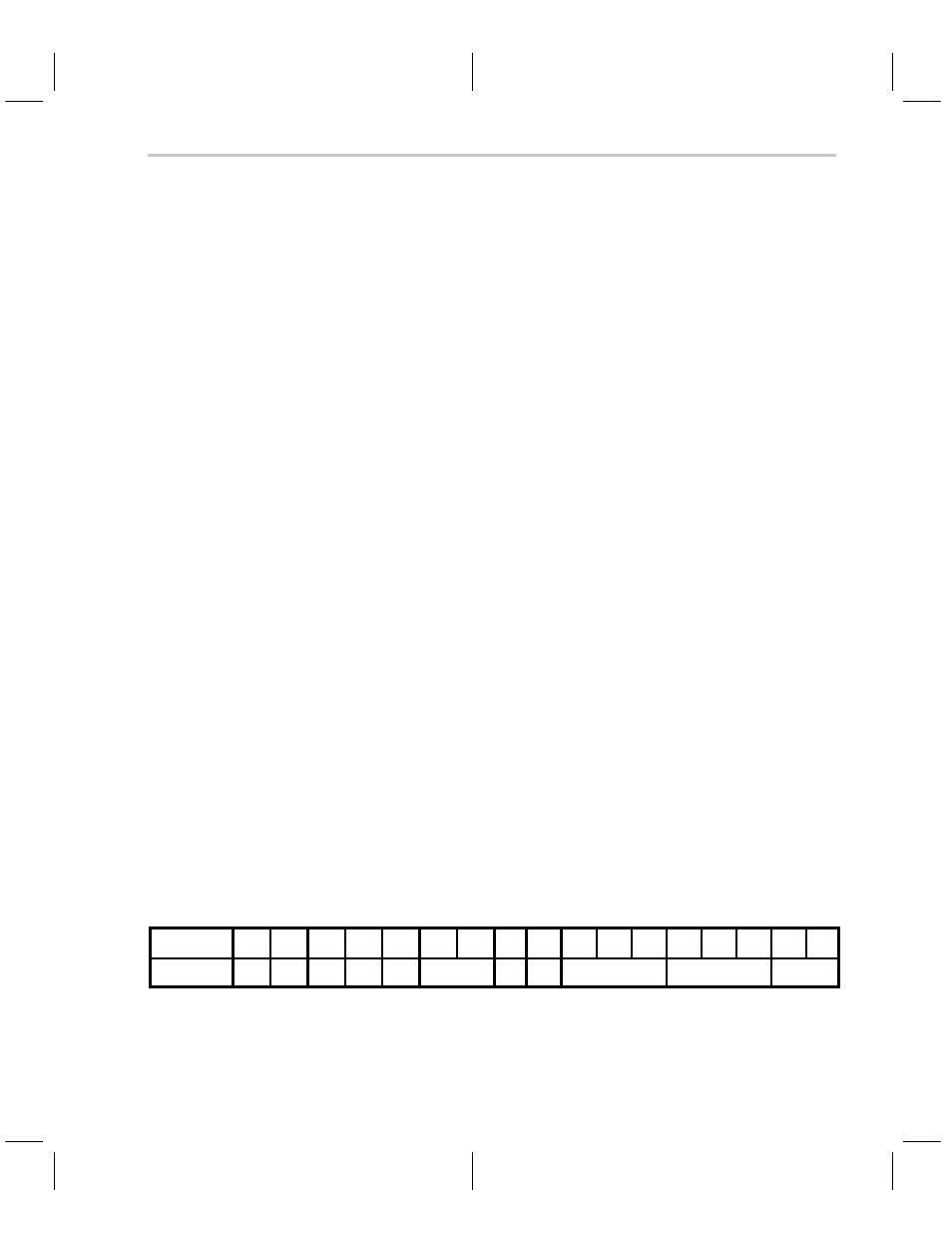

Table 4–2. Addressing Mode Encoding

Bit

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Opcode

next A

am

Rx

pm

am contains addressing mode bits 5 – 7. See Table 4–4 for details.

Rx is the register being used. See for Table 4–3 for details.

pm is the post modification flag. See Table 4–3 for details.

next A is the accumulator pointer premodification field. See Table 4–5 for details.