Texas Instruments MSP50C6xx User Manual

Page 105

Instruction Syntax and Addressing Modes

4-19

Assembly Language Instructions

4.3.7

Flag Addressing

This addressing mode addresses only the 17

th

bit (the flag/tag bit) located in

data memory. This addressing applies to Class 8a instructions as explained

in section 4.4. Using flag addressing, the flag bit can be loaded or saved. In

addition, various logical operations can be performed without affecting the re-

maining 16 bits of the selected word. Two addressing modes are provided. The

first addressing mode, global flag addressing, has bit 0 set to zero and a six

bit field (b1–b6) that defines the flag word address. The second mode, relative

flag addressing, has bit 0 set to one and a 6-bit field (b1–b6) that defines the

flag address relative to R6 (see Figure 4–2). In other words, the, i.e., effective

address = (contents of R6) + (6-bit offset). In flag addressing, R6 contains the

address that points to the 17

th

bit. This should not be confused with byte ad-

dresses and word addresses.

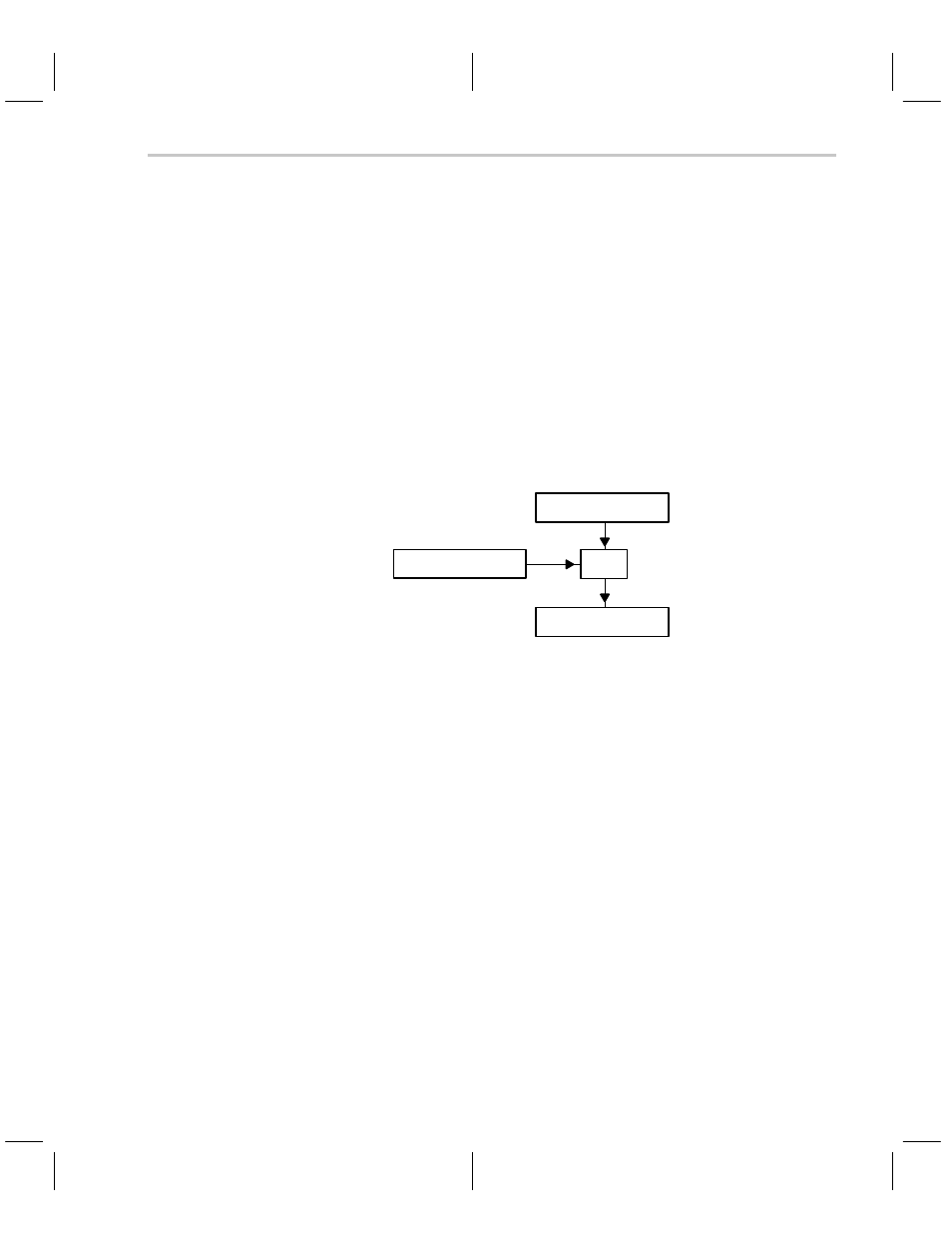

Figure 4–2. Relative Flag Addressing

Address

+

R6

PAGE register

6-Bit positive offset

Operand

Syntax:

name {dest}, {src}

Global Flag:

name TFn, dma6

name dma6, TFn

Relative Flag:

name TFn, *R6+offset6

name *R6+offset6, TFn

Example 4.3.24

MOV *0x02, TF2

Take the test flag 2 bit (TF2 in the status register) and place it into the 17

th

bit

of the data memory location 0x02.

Example 4.3.25

AND TF1, *0x20

AND the test flag 1 bit (TF1 in status register) with the 17

th

bit of the data

memory location 0x20 and store the result in the TF1 bit of the STAT.

Example 4.3.26

OR TF2, *R6+0x02

OR the test flag 2 bit (TF2 in status register) with the 17

th

bit of the data memory

location *(R6+0x02) and store the result in the TF2 bit in of the status register.

So, if R6=0x0100, then relative flag address is 0x0102.

Example 4.3.27

XOR TF1, *R6+0x20

XOR the test flag 1 bit (TF1 in status register) with the 17

th

bit of the data

memory location *(R6+0x20) and store the result in TF1 bit of the status

register. So, if R6=0x0100, then relative flag address is 0x0120.