72 shlspl shift left with subtract pl – Texas Instruments MSP50C6xx User Manual

Page 254

Individual Instruction Descriptions

4-168

4.14.72

SHLSPL

Shift Left With Subtract PL

Syntax

[label]

name

dest, src

[, mod]

Clock, clk

Word, w

With RPT, clk

Class

SHLSPL

An, {adrs}

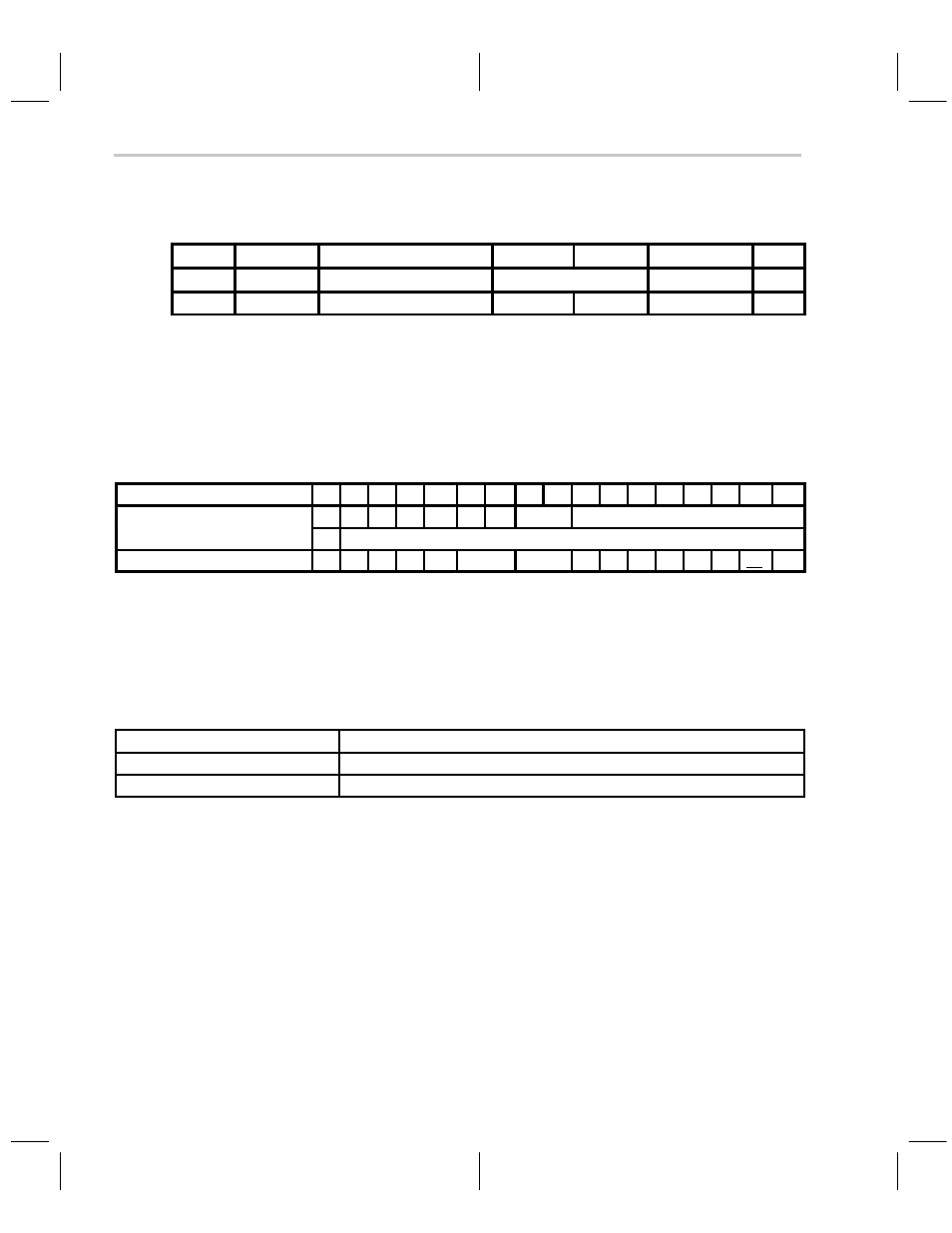

Table 4–46

Table 4–46

1b

SHLSPL

An[~], An[~] [, next A]

1

1

n

R

+3

3

Execution

[premodify AP if mod specified]

PH, PL

⇐

src << SV

dest

⇐

dest – PL

PC

⇐

PC + 1

Flags Affected

OF, SF, ZF, CF are set accordingly

src is {adrs}:

TAG bit is set accordingly

Opcode

Instructions

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

SHLSPL An, {adrs}

0

1

1

1

0

1

0

An

adrs

x

dma16 (for direct) or offset16 (long relative) [see section 4.13]

SHLSPL An[~], An[~] [, next A]

1

1

1

0

0

next A

An

1

1

1

0

0

0

A~

~A

Description

Premodify the accumulator pointer if specified. Shift accumulator or data memory

value pointed by {adrs} to left n

SV

bits (as specified by the SV register) into a 32-bit

result. This result is zero-filled on the right and either zero-filled or sign-extended on

the left (based on the setting of the extended sign mode (XM) bit in the status register).

The upper 16 bits are latched into the product high (PH) register. The lower 16 bits of

the result [product low (PL) register] is subtracted from the destination accumulator (or

its offset). This instruction propagates the shifted bit to the next accumulator.

Syntax

Description

SHLSPL An, {adrs}

Shift data memory word left, substract PL from An

SHLSPL An[~], An[~] [, next A]

Shift An[~] left, substract PL to An[~]

See Also

SHLSPLS, SHLTPL, SHLTPLS, SHLAPL, SHLAPLS

Example 4.14.72.1

SHLSPL A0, *R4++R5

Shift the word pointed by the byte address stored in R4 by n

SV

bits to the left, subtract the shifted (PL)

from Accummulator A0, and store the result in accumulator A0. Add R5 to R4 and store result in R4

PH holds the upper 16 bits of the shift.

Example 4.14.72.2

SHLSPL A2, *R1++

Shift the word pointed by the byte address stored in R1 by n

SV

bits to the left, subtract the shifted value

(PL) from the accumulator A2, and store the result in accumulator A2. Increment R1 (by 2). PH holds

the upper 16 bits of the shift.

Example 4.14.72.3

SHLSPL A1, A1, ++A

Preincrement accumulator pointer AP1. Shift the accumulator A1 by n

SV

bits to the left, subtract PL from

A1, and store result in accululator A1. After execution PH contains the upper 16 bits of the 32-bit shift.