Texas Instruments MSP50C6xx User Manual

Page 68

I/O

3-4

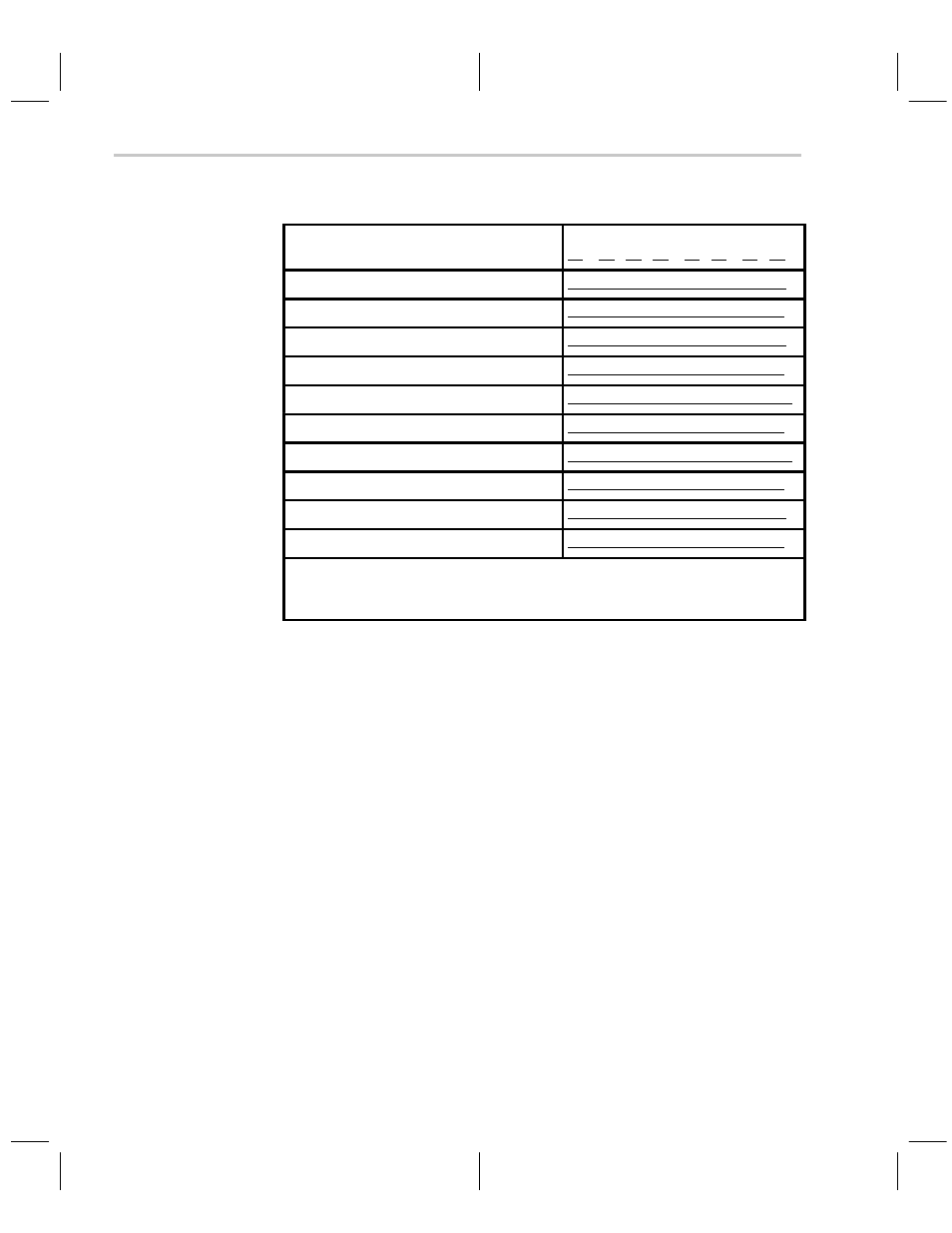

The following table shows the bit locations of the I/O port mapping:

(8-bit wide location)

07 06 05 04 03 02 01 00

A port data register

address 0x00

. . . . .

A7 A6 A5 A4 A3 A2 A1 A0

A port control register

address 0x04

. . .

C C C C C C C C

B port data register

address 0x08

. . . . .

B7 B6 B5 B4 B3 B2 B1 B0

B port control register

address 0x0C

. . .

C C C C C C C C

C port data register

address 0x10

. . . . .

C7 C6 C5 C4 C3 C2 C1 C0

C port control register

address 0x14

. . .

C C C C C C C C

D port data register

address 0x18

. . . . .

D7 D6 D5 D4 D3 D2 D1 D0

D port control register

†

address 0x1C

. .

C C C C C C C C

E port data register

address 0x20

. . . . .

E7 E6 E5 E4 E3 E2 E1 E0

E port control register

address 0x24

. . .

C C C C C C C C

A7, B7, C7, D7, E7 : data register

C

: control register (0 = IN, 1 = OUT)

0x00

: state of control register after RESET low

† Ports D4 and D5 may be dedicated to the Comparator function, if the Comparator Enable bit is

set. If so, then bits 4 and 5 of the D port Control register must be CLEAR. Please refer to Section

3.3, Comparator, for details.

Port D

0

is connected to the branch condition COND1. Port D

1

is connected to

the branch condition COND2, assuming the comparator is disabled. Please

refer to Section 3.1.4, Branch on D Port, (and to Section 3.3, Comparator) for

more information. External interrupts can be detected when transitions occur

on ports D

2

, D

3

, D

4

, and D

5

. The interrupts associated with the D port are

supported whether those pins are programmed as inputs or as outputs.

3.1.2

Dedicated Input Port F

Port F is an 8-bit wide input-only port. The data presented to the input pin can

be read by referring to the appropriate bit in the F port data register, address

0x28. This is done using the IN instruction, with the 0x28 address as an

argument. The state of the F port data registers is not initialized with RESET.

After RESET is taken high, the state of the F port data register is unknown.

Each of the pins at port F has a programmable pull-up resistor. All eight pullup

resistors can be enabled by setting the enable pullup (EP) in the interrupt/gen-

eral control register (IntGenCtrl). The address of the IntGenCtrl is 0x38, and

the location of the EP bit is 12. Clearing the EP bit disables the eight pullups,