9 timer registers – Texas Instruments MSP50C6xx User Manual

Page 55

Timer Registers

2-31

MSP50C6xx Architecture

This software-controlled trim for the RTO is not a replacement for the external

reference-resistor mounted at pins OSC

IN

and OSC

OUT

. Also, note that this

adjustment has no effect on the rate of the CRO reference oscillator.

2.9

Timer Registers

The C6xx contains two identical timers, TIMER1 and TIMER2. Each includes

a period register and a count-down register. The period register (PRD1 or

PRD2) defines the initial value for the counter, and the count-down register

(TIM1 or TIM2) does the counting. When the count-down register decrements

to the value 0x0000, then the value currently stored in the period register is

loaded to the count-down register. The count-down register then resumes

counting again from that value.

For each TIMER, there is an interrupt-trigger event associated with the

TIMER’s underflow condition (the point of reaching 0x0000 and then re-setting

again). When enabled, the interrupt INT1 is triggered by the underflow of

TIMER1, and the interrupt INT2 is triggered by the underflow of TIMER2. INT1

and INT2 are the second and third-highest priority interrupts in the C6xx. Refer

to Section 2.7, Interrupt Logic, for a summary of the interrupt logic, and to

Section 2.6.3, Interrupt Vectors, for a listing of the interrupt vectors.

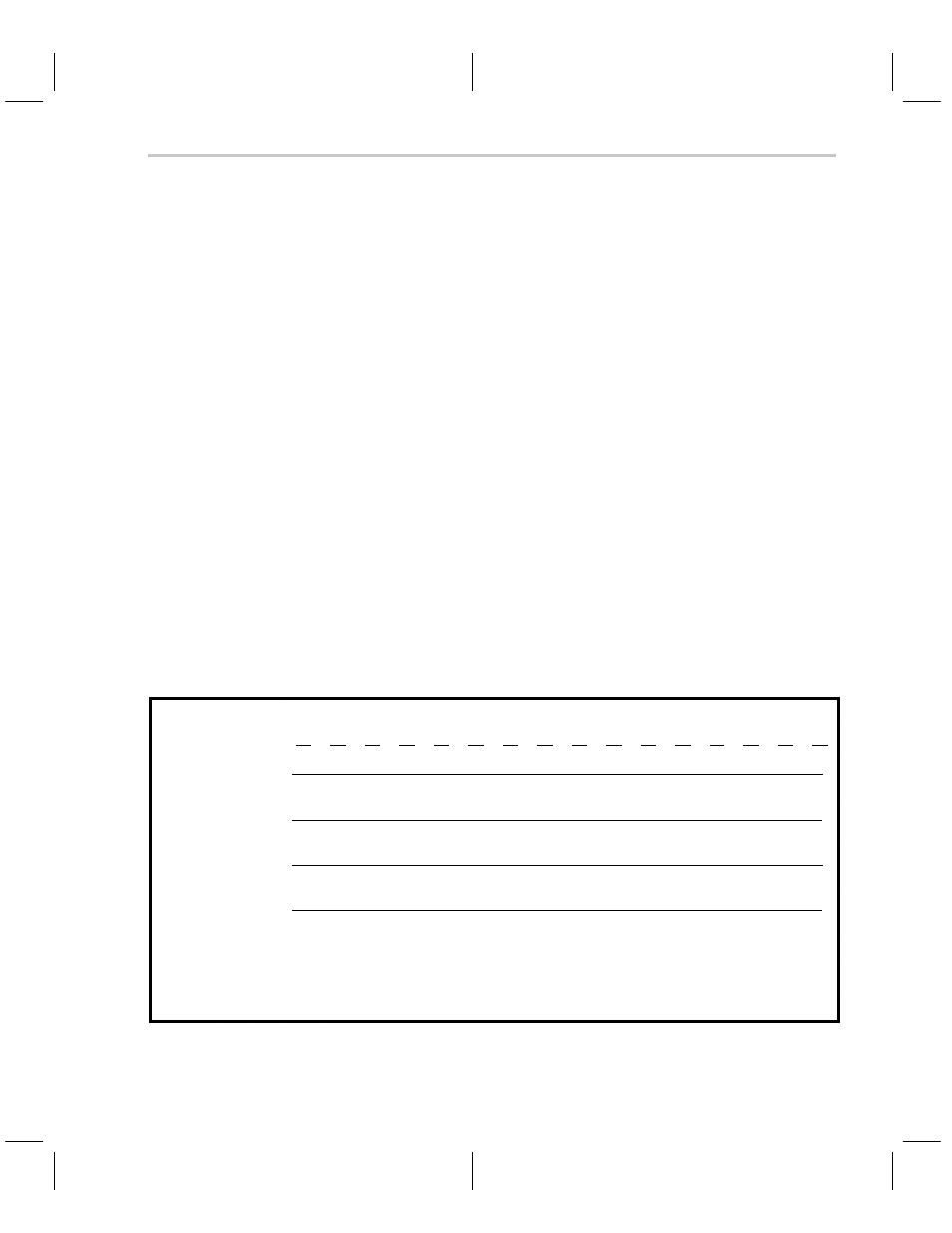

Both the period and the count-down registers are readable and writeable as

port-addressed registers:

(16-bit wide location)

15

14

13

12

11

10

09

08

07

06

05

04

03

02

01

00

PRD1 register

†

address 0x3A

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

TIMER1 Period

TIM1 register

†

address 0x3B

T

T

T

T

T

T

T

T

T

T

T

T

T

T

T

T

TIMER1 Count-Down

Triggers INT1 on underflow

PRD2 register

address 0x3E

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

TIMER2 Period

TIM2 register

address 0x3F

T

T

T

T

T

T

T

T

T

T

T

T

T

T

T

T

TIMER2 Count-Down

Triggers INT2 on underflow

P : period register (initial counter value)

T : count-down register (counts from the value in P)

0x0000 : default state of both registers after RESET LOW

† TIMER1 may be associated with the comparator function, if the comparator enable bit is set. Refer to Section 3.3, Comparator,

for details.