Texas Instruments MSP50C6xx User Manual

Page 116

Instruction Classification

4-30

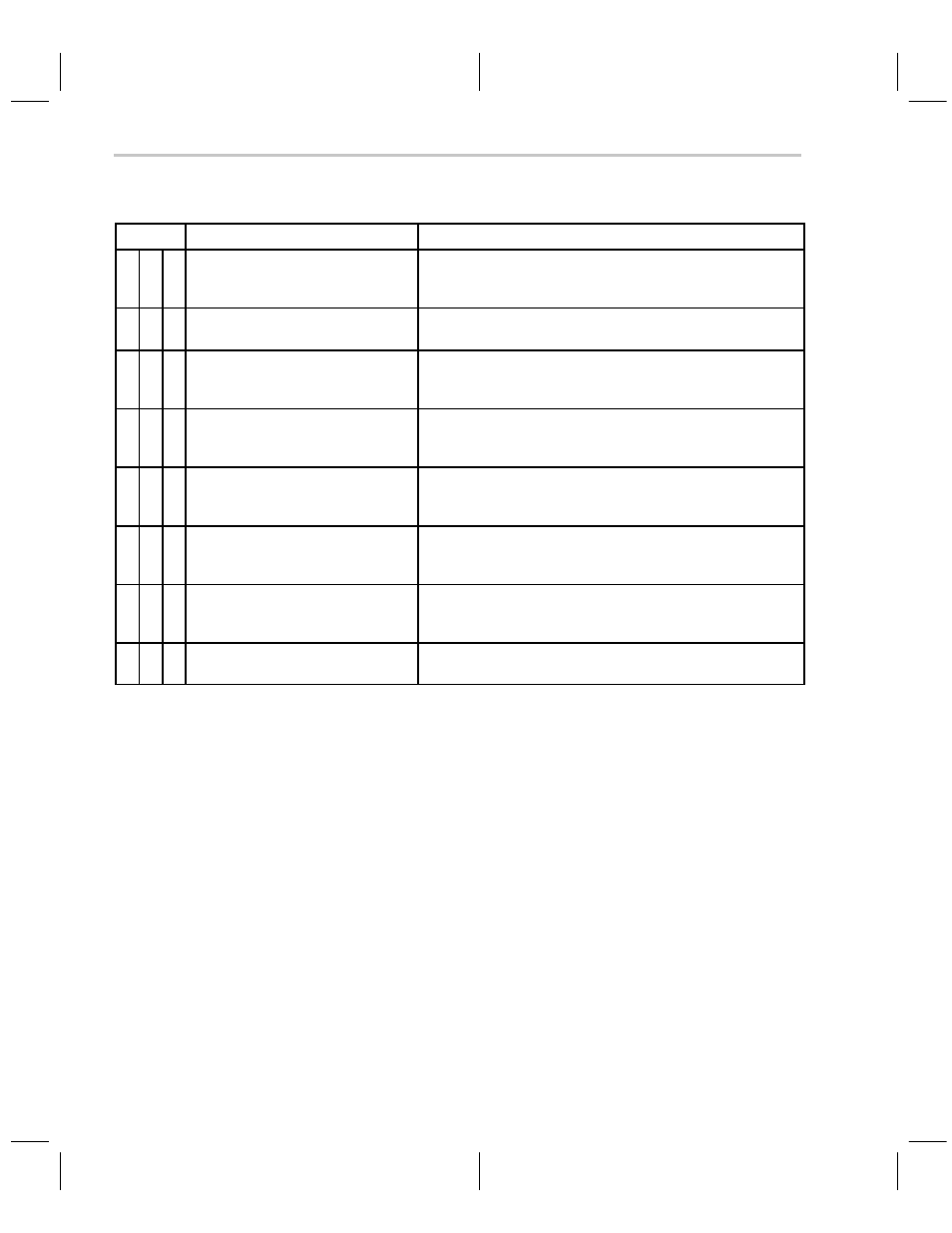

Table 4–18. Class 2b Instruction Description

C2b

Mnemonic

Description

0

0

0

ADD An[~], An[~], imm16 [, next A]

ADDS An[~], An[~], pma16

Add long constant to accumulator (or offset accumulator if

A~=1) and store result to accumulator (~A=0) or offset

accumulator (~A=1). ALU status modified.

0

0

1

MOV An[~], imm16 [, next A]

MOVS An[~], pma16

Load long constant to accumulator (~A=0 or 1). ALU status is

modified.

0

1

0

SUB An[~], An[~], imm16 [, next A]

SUBS An[~], An[~], pma16

Subtract a long constant from the accumulator (A~=0 or 1).

Store the result in accumulator (~A=0) or offset accumulator

(~A=1). ALU status is modified.

0

1

1

CMP An[~], imm16 [, next A]

CMPS An[~], pma16

Modify ALU status by subtracting a long constant from accu-

mulator (A~=0) or from offset accumulator (A~=1). Neither ac-

cumulator or offset accumulator is modified

1

0

0

OR An[~], An[~], imm16 [, next A]

ORS An[~], An[~], pma16

Logical OR a long constant with accumulator (A~=0 or 1).

Store the result in accumulator(~A=0) or offset accumulator

(~A=1). ALU status is modified.

1

0

1

AND An[~], An[~], imm16 [, next A]

ANDS An[~], An[~], pma16

Logical AND a long constant with accumulator (A~=0 or

1).Store the result to accumulator(~A=0 or 1) . ALU status is

modified.

1

1

0

XOR An[~], An[~], imm16 [, next A]

XORS An[~], An[~], pma16

Logical exclusive OR a long constant with accumulator (A~=0

or 1) Store the result to accumulator (~A=0 or 1). ALU status is

modified.

1

1

1

MOV MR, imm16 [, next A]

Load a long constant to MR in signed mode. No change in

status.

4.4.3

Class 3 Instruction: Accumulator Reference

These instructions reference the accumulator and, in some instances, specific

registers for transfers. Some instructions use a single accumulator operand

and others use both the accumulator and the offset accumulator to perform

operations between two accumulator values. The A~ bit in the instruction word

reverses the sense of the addressed accumulator and the addressed offset

accumulator. In general, if A~=1, the instruction uses the offset accumulator

as the input operand on single accumulator operand instructions. It

interchanges the arithmetic order (subtract, compare, multiply–accumulate,

etc.) of the two operands when both are used. Exceptions to the rule are the

instructions NEGAC[S], NOTAC[S], MULSPL[S], MULAPL[S], MULTPL[S],

SHLSPL[S], SHLTPL[S] and SHLAPL[S], which use the reverse A~ control

(A~=1 for accumulator, A~=0 for offset accumulator). The ~A bit in the

instruction word controls the destination of the result to be the accumulator

(~A=0) or the offset accumulator (~A=1).

In addition to basic accumulator arithmetic functions this class also includes

an accumulator lookup instruction and several register transfer instructions