Texas Instruments MSP50C6xx User Manual

Page 129

Instruction Classification

4-43

Assembly Language Instructions

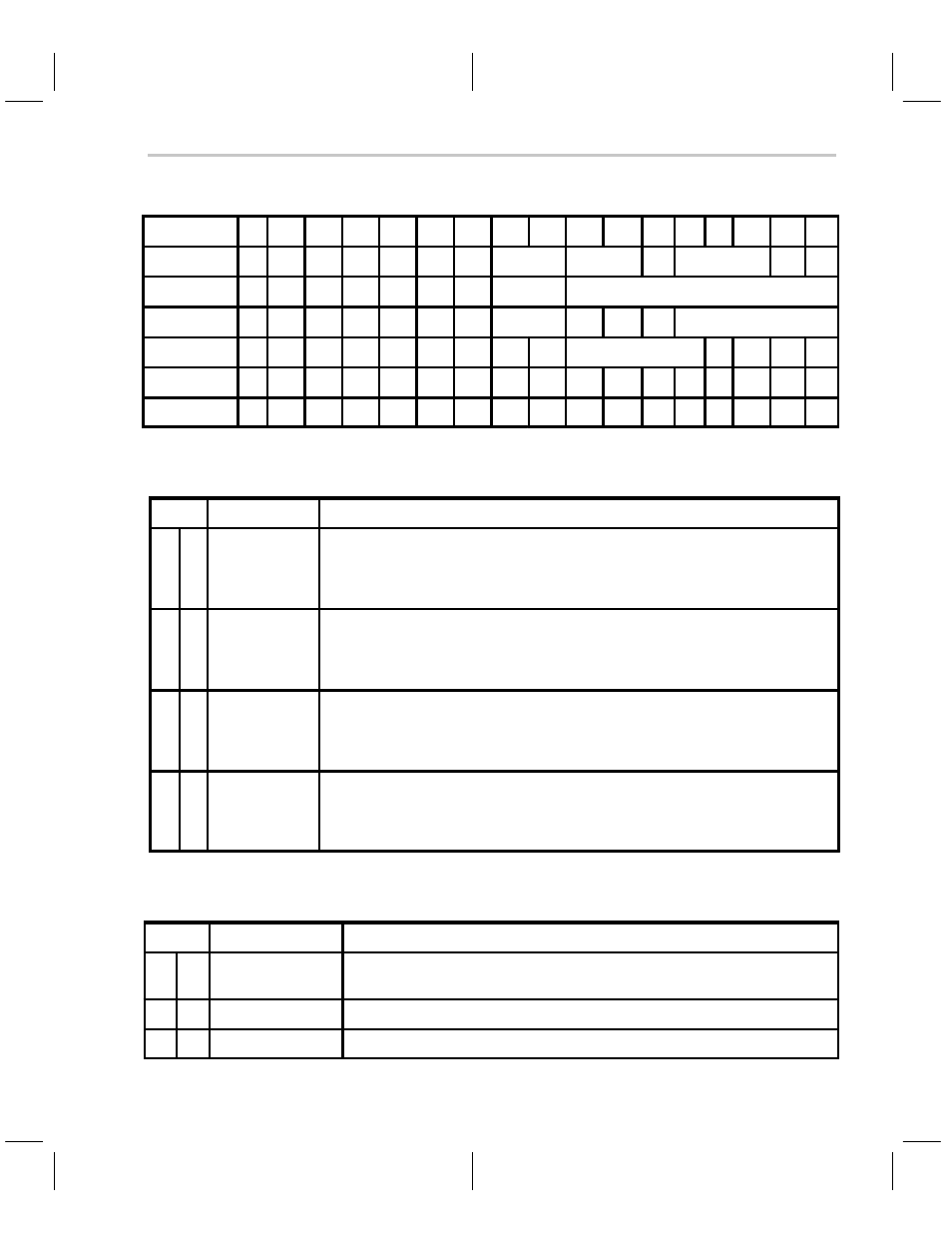

Table 4–35. Class 9a Instruction Encoding

Bit

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Class 9a

1

1

1

0

1

0

0

An

C9a

0

Rx

1

1

Class 9b

1

1

1

1

1

1

0

C9a

imm8

Class 9c

1

1

1

1

1

0

1

APn

0

C9c

x

imm5

Class 9d

1

1

1

1

1

1

1

1

0

C9d

0

0

0

0

ENDLOOP n

1

1

1

1

1

1

1

1

0

0

0

0

1

0

0

0

n

NOP

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

Table 4–36. Class 9a Instruction Description

C9a

Mnemonic

Description

0

0

FIRK An, *Rx

Finite impulse response tap execution. When used with repeat counter will execute a

16 bit

×

16 bit multiplication between an indirect-addressed data memory buffer and

program memory (coefficients). 32-bit accumulation. Circular buffering. Each tap

executes in 2 cycles. Rx automatically increments by 2 per tap.

0

1

FIR An, *Rx

Finite impulse response tap execution. When used with the repeat counter, it will

execute a 16 bit

×

16 bit multiplication between two indirect-addressed data memory

buffers into a 32-bit accumulator. Circular buffer operation. Executes in 2 instruction

cycles. Rx and R(x+1) automatically increments by 2 per tap.

1

0

CORK An, *Rx

Correlation function. When used with repeat will execute 16

×

16 multiplication

between data memory and program memory, 48-bit accumulation, and a circular

buffer operation. Each tap takes 3 instruction cycles. Rx automatically increments by

2 per tap.

1

1

COR An, *Rx

Correlation function. When used with repeat will execute 16

×

16 multiplication

between two indirectly addressed data memory buffers, 48-bit accumulation, and a

circular buffer operation. Each tap takes 3 instruction cycles. Rx and R(x+1)

automatically increments by 2 per tap.

Table 4–37. Class 9b Instruction Description

C9b

Mnemonic

Description

0

0

RPT imm8

Load the repeat counter with an 8-bit constant and execute the instruction

that follows imm8+2 times. Interrupts are queued during execution.

0

1

MOV STR, imm8

Load the STR register with an 8-bit constant.

1

0

MOV SV, imm4

Load the SV (shift value) register with a 4-bit constant.