Texas Instruments MSP50C6xx User Manual

Page 124

Instruction Classification

4-38

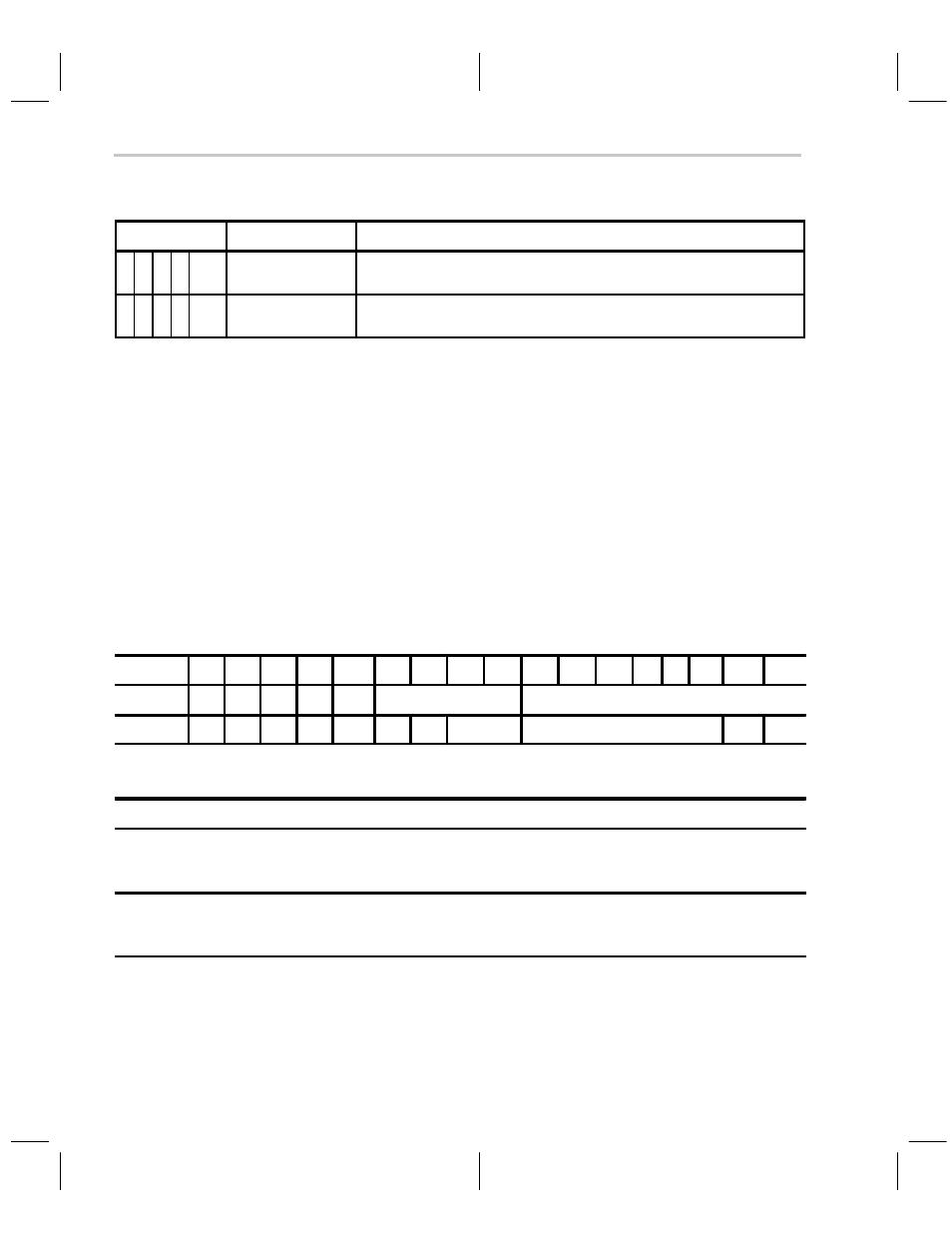

Table 4–27. Class 5 Instruction Description (Continued)

C5

Mnemonic

Description

1 1 1 1

0

RPT {adrs}

8

Load repeat counter with lower 8 bits of data memory location referred by

addressing mode {adrs}. Interrupts are queued during execution.

1 1 1 1

1

MOV STAT, {adrs}

Load status (STAT) register with effective data memory location referred

by addressing mode {adrs} (17 bits with TAG).

4.4.6

Class 6 Instructions: Port and Memory Reference

These instructions provide the basic expansion port of the MSP50P614/

MSP50C614 processor. IN instructions transfer 16-bit data from one of 16

expansion ports. OUT instructions transfer 16-bit data to one of the 16

expansion ports. In a typical system, the expansion ports are divided into those

that serve internal peripheral functions and those that serve external pins. For

subclass 6b, IN and OUT provide bidirectional transfers between the same

port address (16) and accumulator. In addition, IN and OUT instructions in

class 6b can communicate with an extra 48 ports (a total of 64 including the

shared ports). Class 6b instructions also have reference to the string bit for

checking the arithmetic status of a string transfer.

Table 4–28. Class 6a Instruction Encoding

Bit

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Class 6a

1

1

0

0

C6a

port4

adrs

Class 6b

1

1

1

0

1

1

s

An

port6

C6b

~A~

Table 4–29. Class 6a Instruction Description

C6a

Mnemonic

Description

0

IN {adrs}, port4

Transfer a 16-bit value of addressed port to data memory location referred

by addressing mode {adrs}. Refer to port address map. Transfer status is

modified.

1

OUT port4, {adrs}

Transfer a 16-bit value in the data memory location referred by addressing

mode {adrs} to addressed port. Refer to Port address map. Transfer is sta-

tus modified.