Texas Instruments MSP50C6xx User Manual

Page 294

Instruction Set Summay

4-208

Assembly Language Instructions

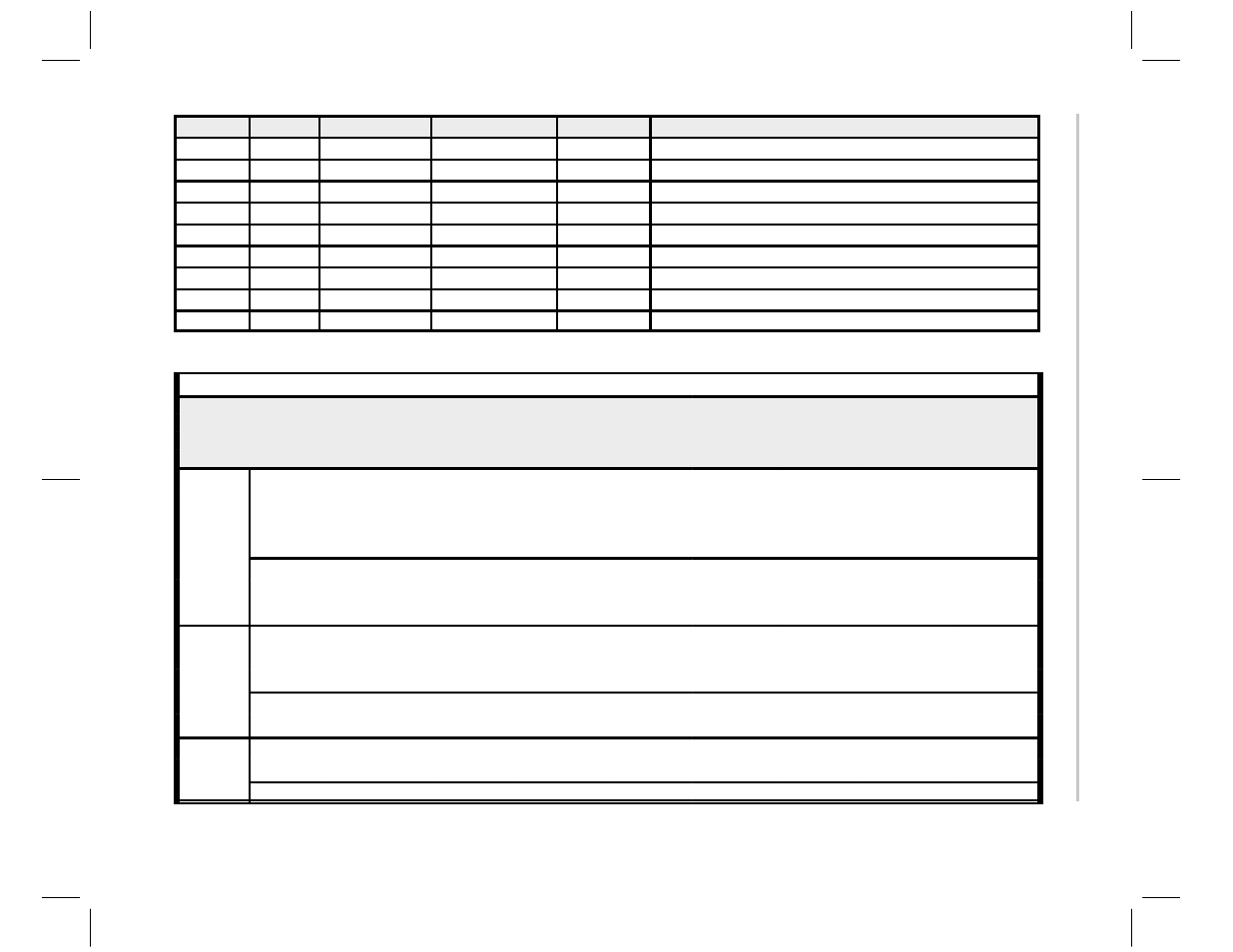

Interrupt

Vector

Source

Trigger Event

Priority

Comment

INT0

0x7FF0

DAC Timer

timer underflow

highest

used to synch. speech data

INT1

0x7FF1

TIMER1

timer underflow

2nd

INT2

0x7FF2

TIMER2

timer underflow

3rd

INT3

0x7FF3

port PD2

rising edge

4th

port PD2 goes HIGH

INT4

0x7FF4

port PD3

falling edge

5th

port PD3 goes LOW

INT5

0x7FF5

all port F

any falling edge

6th

F port goes from all–HIGH to LOW

INT6†

0x7FF6

port PD4

rising edge

7th

port PD4 goes HIGH

INT7†

0x7FF7

port PD5

falling edge

lowest

port PD5 goes LOW

RESET

0x7FFF

hardware RESET

active low pulse

nonmaskable

Some internal I/O register

† INT6 and INT7 may be associated instead with the Comparator function, if the Comparator Enable bit has been set. Refer to section 3.3 for details

8 kHz Nominal Synthesis Rate (32.768 kHz oscillator reference)

ClkSpdCtrl

Output

Number of

Number of

IntGenCtrl

ClkSpdCtrl

PLLM

Master Clock

PDM

CPU Clock

Output

Sampling

Number of

Instructs

Number of

Instructs

DAC

P

i i

PDMCD

Bi

Over-Sampling

F

Register

Rate

(H )

Rate

(H )

Rate

(H )

p

g

Rate

btwn DAC

btwn 8 kHz

Precision

Bit

Factor

Value

(Hz)

(Hz)

(Hz)

(Hz)

Interrupts

Interrupts

8 bits

1

1x

0x 0F

2.10 M

2.10 M

1.05 M

8.19 k

128

128

2x

0x 1E

4.06 M

4.06 M

2.03 M

15.87 k

128

256

4x

0x 3E

8.26 M

8.26 M

4.13 M

32.26 k

128

512

8x

0x 7C

16.38 M

16.38 M

8.19 M

64.00 k

128

1024

0

1x

0x 1E

4.06 M

2.03 M

2.03 M

7.94 k

256

256

2x

0x 3E

8.26 M

4.13 M

4.13 M

16.13 k

256

512

4x

0x 7C

16.38 M

8.19 M

8.19 M

32.00 k

256

1024

9 bits

1

1x

0x 1E

4.06 M

4.06 M

2.03 M

7.94 k

256

256

2x

0x 3E

8.26 M

8.26 M

4.13 M

16.13 k

256

512

4x

0x 7C

16.38 M

16.38 M

8.19 M

32.00 k

256

1024

0

1x

0x 3E

8.26 M

4.13 M

4.13 M

8.06 k

512

512

2x

0x 7C

16.38 M

8.19 M

8.19 M

16.00 k

512

1024

10 bits

1

1x

0x 3E

8.26 M

8.26 M

4.13 M

8.06 k

512

512

2x

0x 7C

16.38 M

16.38 M

8.19 M

16.00 k

512

1024

0

1x

0x 7C

16.38 M

8.19 M

8.19 M

8.00 k

1024

1024