A n 9 3 – Silicon Laboratories SI2493/57/34/15/04 User Manual

Page 32

A N 9 3

32

Rev. 1.3

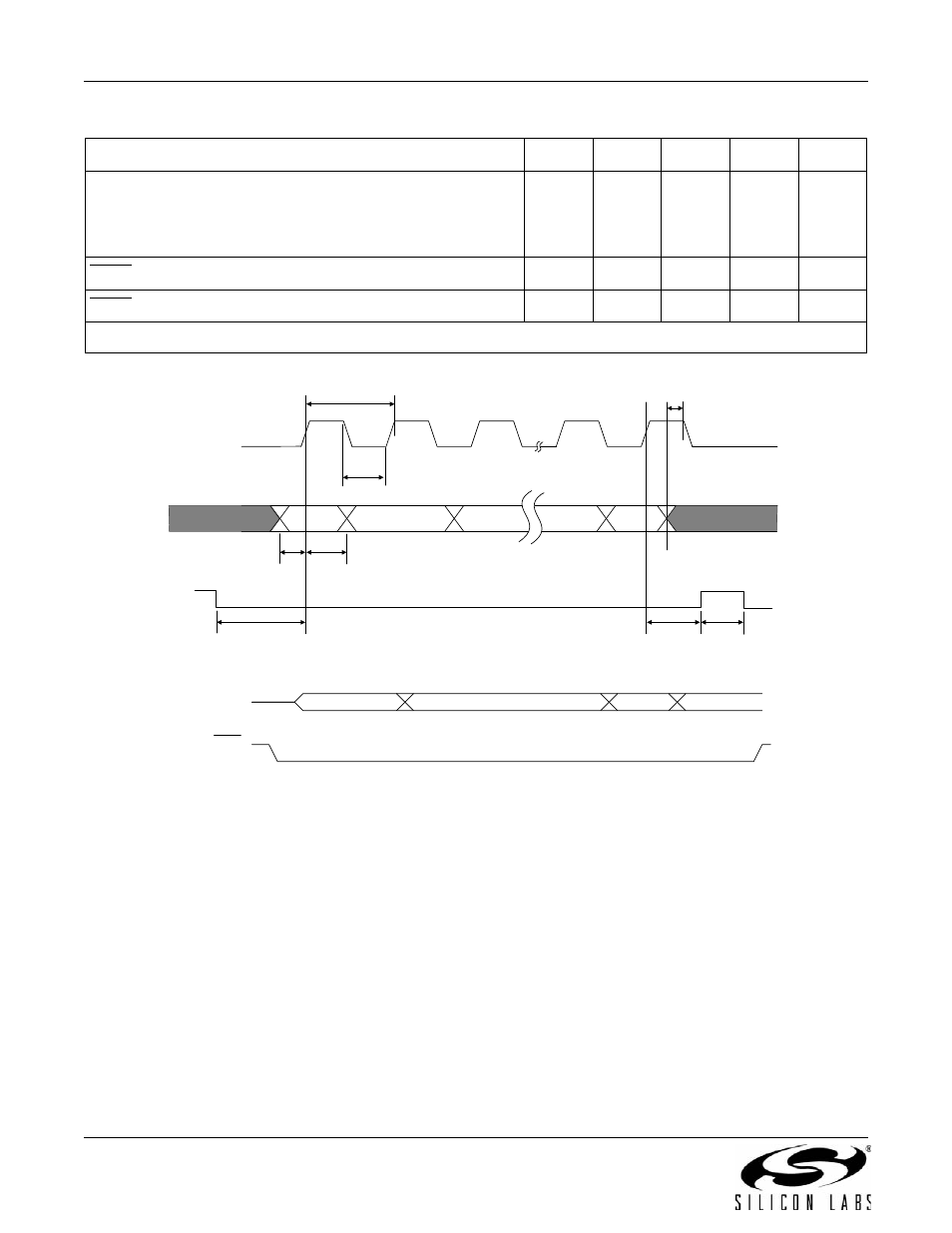

Figure 11. EEPROM Serial I/O Timing

EESD tristated before last falling EECLK edge during read

cycle. Last positive half of EECLK cycle is extended to provide

both 500 ns minimum EOH and 100 ns EESD before EECLK

falling edge.

EOZ

100

—

—

ns

EECS disable time between accesses

ECSW

500

—

—

ns

EECS asserted after final EECLK edge

ECSH

1

—

—

µs

*Note:

EESD

output at negative EECLK edge

Table 28. EEPROM Timing

Parameter

Symbol

Min.

Typ.

Max.

Unit

ECLK

LSB

MSB

EISU

EOSU

EIH

EDH

ECSH

ECSW

EOZ

ECSS

EEPROM Data Format

EESD

EECS

8-bit instruction

16-bit address

8-bit data

EOH

This manual is related to the following products: