A n 9 3 – Silicon Laboratories SI2493/57/34/15/04 User Manual

Page 28

A N 9 3

28

Rev. 1.3

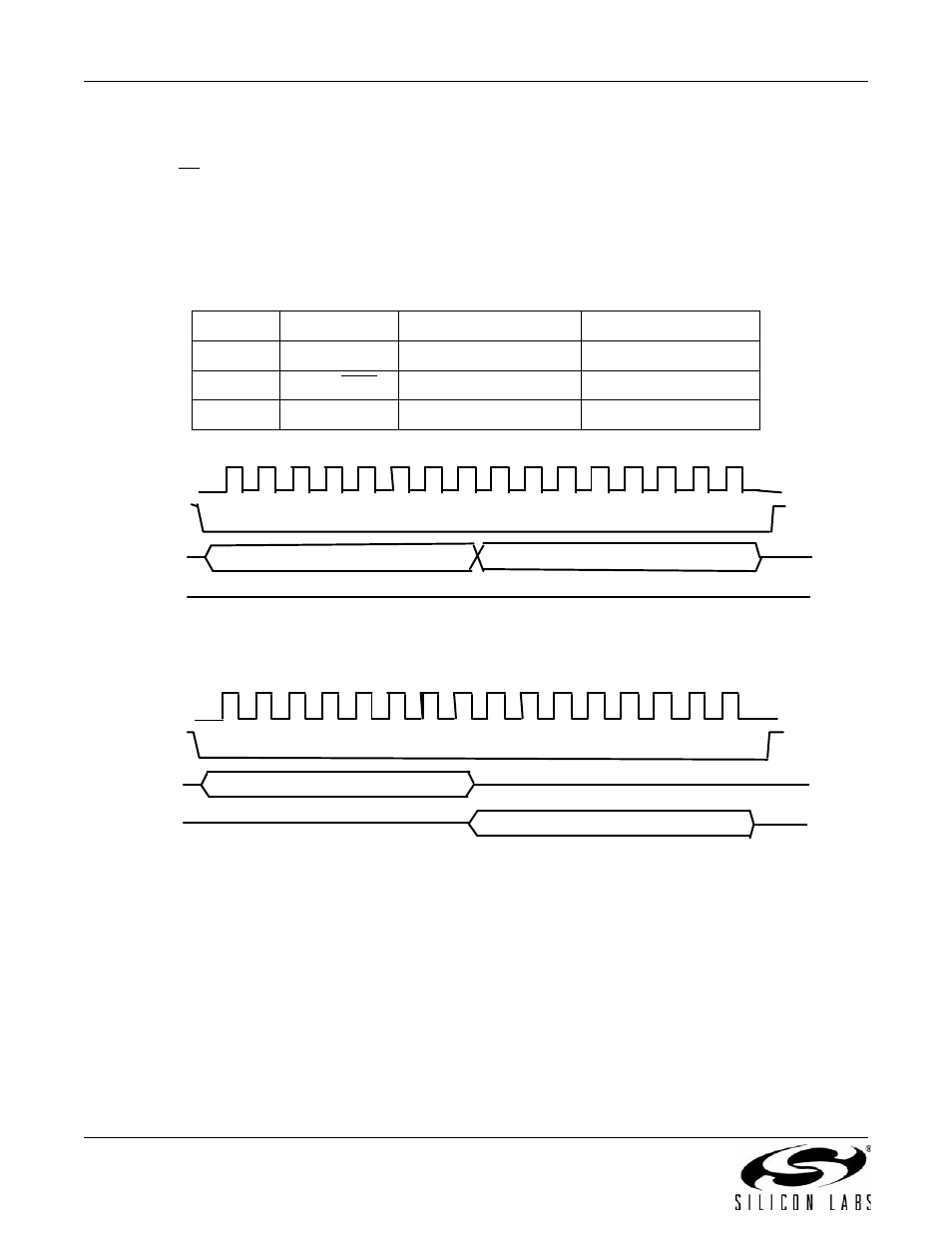

2.2.4.4. SPI Interface Operation

SPI interface operation is supported in the Si2493/57/34/15/04 Revision D or later and the Si2494/39 Revision A or

later. When the device is powered up for SPI interface, the modem becomes an SPI slave, and the pins are

configured to SS (chip select input, active low), MOSI (serial data input to modem), MISO (serial data output from

modem) and SCLK (serial data clock input). The HIR0 and HIR1 registers described above are also available in

SPI mode. Each SPI operation consists of a control-and-address byte and a data byte. The bit definitions of the

control-and-address byte are shown in Table 24. The timing diagrams that follow show SPI read and write

waveforms. Refer to the device data sheet for timing characteristics.

Figure 9. SPI Read and Write Timing Diagrams

2.2.4.5. Interface Communication Modes

Data flow control is implemented in the SPI and parallel interfaces differently from UART mode. When parallel or

SPI mode is selected, data communication may be driven by interrupts or by polling. Refer to "Appendix C—

Parallel/SPI Interface Software Implementation" on page 290 for implementation details for both methods. The

parallel and SPI interfaces have four sources of interrupts and only one interrupt pin. The four interrupts are:

1. RXF Interrupt: receive FIFO almost full

2. TXE Interrupt: transmit FIFO almost empty

3. Timer Interrupt: receive FIFO not empty

4. U70 Interrupt: various conditions, such as ringing, parallel phone pickup, etc. as defined in register U70

The source of the interrupt can be determined by reading HIR1.

Table 24. SPI Control-and-Address Bit Definitions

Bit

Function

Meaning when High

Meaning when Low

7

Address

Access HIR1

Access HIR0

6

Read/Write

Read register

Write register

5:0

Reserved

Not allowed

Must be all zeroes

SCK

NSS

MISO

MOSI

Hi‐Z

Hi‐Z

SPI 2‐Byte Write Protocol

Address/Control

Data

SCK

NSS

MISO

MOSI

Hi‐Z

Hi‐Z

SPI 2‐Byte Read Protocol

Address/Control

Data