2 audio and power, Audio and power -23 – Motorola SSETM 5000 User Manual

Page 45

6881094C12-A

November 11, 2004

Theory of Operation: VOCON Board

2-23

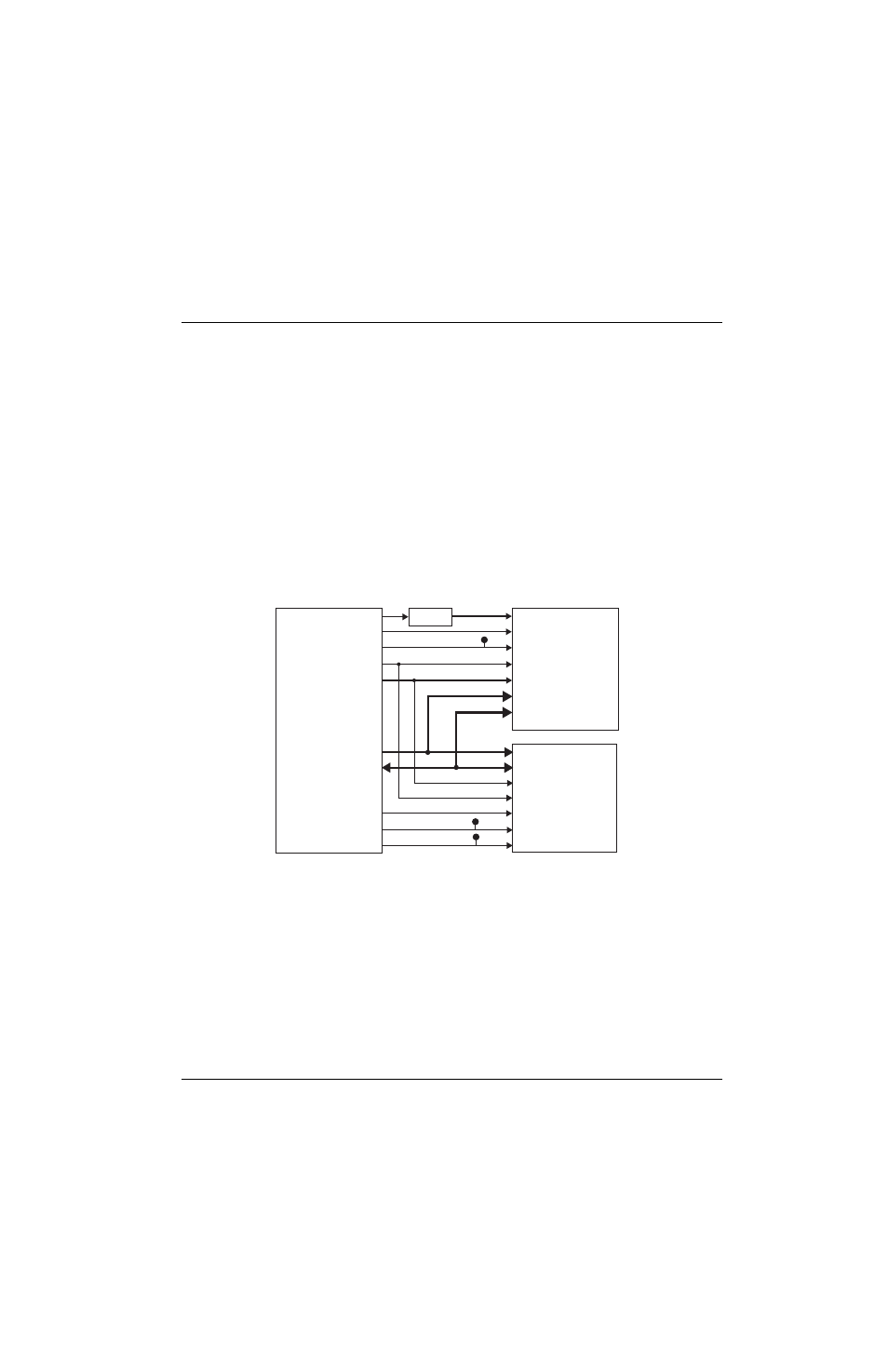

the Address(23:0) and Data(15:0) busses. The Flash memory contains host firmware, DSP firmware,

and codeplug data with the exception of the tuning values that reside on the transceiver board’s

serial EEPROM. The Flash memory IC is not field repairable.

The RESET_OUT of the dual-core processor is at a GPIO voltage logic level. Components D401 and

R401 are used to convert the voltage down to a 1.8 V logic level, and this 1.8 V reset signal is fed to

the Flash RESET pin. When this pin is asserted (active low logic), the Flash is in reset mode. In this

mode, the internal circuitry powers down, and the outputs become high-impedance connections.

The Flash active-low chip select pin, EN_CE, is connected to the active-low CS0_N pin (CS0 test

point) of the EIM. When the EN_CE is not asserted, the Flash is in standby mode, which reduces

current consumption.

Several other active-low control pins determine what mode the Flash memory is in: the address valid

pin ADV that is connected to the EIM LBA_N signal, the output enable pin EN_OE that is connected

to the EIM OE_N signal, and the write enable pin EN_WE that is connected to the EIM EB1_N

signal. For read mode, the ADV and EN_OE pins are asserted while the EN_WE pin is not asserted.

When the EN_WE is asserted and the EN_OE pin is unasserted, the Flash operates in the write

mode.

illustrates the EIM and memory ICs block diagram.

Figure 2-8. Dual-Core Processor EIM and Memory Block Diagram

2.5.2.2 Audio and Power

The audio and power section contains the following components:

• GCAP II IC U501

• 5 V regulator U505

• 1.55 V regulator

• Audio pre-amplifier U502

• Audio power amplifier (PA) U503

• EEPOT U509

Dual-Core

Processor

U401

Flash

U402

SRAM

U403

RESET_OUT

LBA_N

CS0_N

EB1_N

OE_N

A(23:0)

D(15:0)

EB0_N

CS2_N

RW_N

Voltage

Translator

RESET

ADV

EN_CE

EN_WE

EN_OE

A(22:0)

D(15:0)

A(18:0)

D(15:0)

EN_OE

LB

UB

CS1

EN_WE

CSO

A(23:1)

A(19:1)

CS2

R_W

MAEPF-27414-A