Force10 Networks PSeries 100-00055-01 User Manual

Page 95

P-Series Installation and Operation Guide, version 2.3.1.2

95

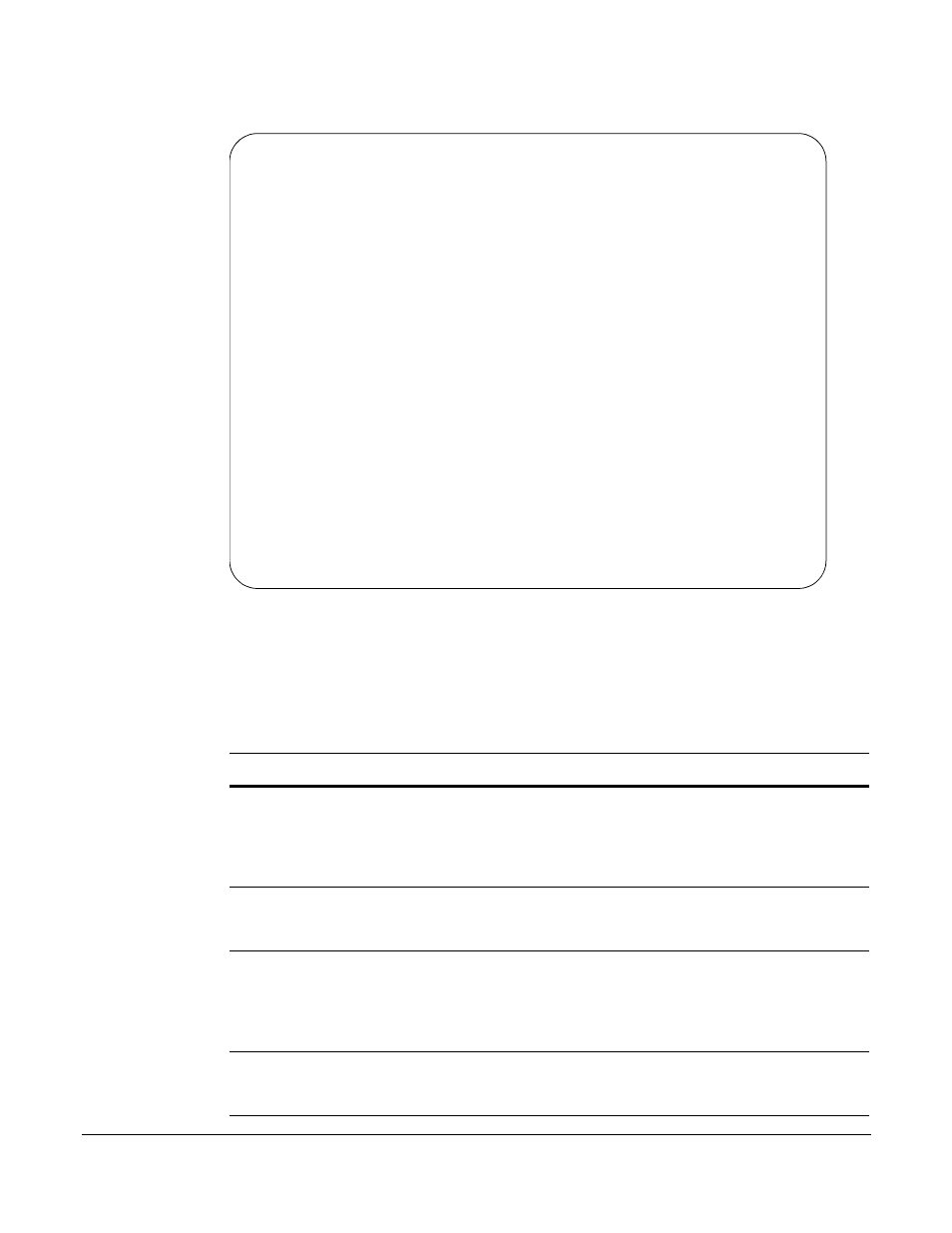

Example

Figure 59

[root@localhost ~]# pnic loadconf

No card number specified. Assuming card 0

Loading configurations ...

Read from configuration file and apply to PNIC card...

Registers on master FPGA:

(0x10)0000 (0x14)0010 (0x18)0000

Registers on PCI FPGA:

(0x18)0100 (0x24)20788 (0x28)20788

DMA Capture : on

MAC rewrite : CH0 - disabled; CH1 - disabled

Default Drop packet : disabled

Temporary memory : enabled

Aggregate mode : enabled

Flow teardown : disabled

PHY passive mode : disabled

Vlan remove : disabled

Read out the registers that were just applied.

On MASTER FPGA

(0x10)00000000 (0x14)00000010 (0x18)00000000

On PCI FPGA

(0x18)00000100 (0x24)00020788 (0x28)00020788

DMA Capture : on

MAC rewrite : CH0 - disabled; CH1 - disabled

Default Drop packet : disabled

Temporary memory : enabled

Aggregate mode : enabled

PHY passive mode : disabled

Flow teardown : disabled

Vlan remove : disabled

Version : P_PRIV2.3.0.010

pnic loadconf Command Example

Usage

Information

The syntax of such parameter files is (

address

)

value

where

address

is the decimal address

of the DPI control register, and

value

is the hexadecimal parameter to be loaded.

shows the parameters to which each address is mapped.

Table 26 pnic loadconf Address Mapping

Address

Corresponding Parameter

Address 20

(Master FPGA)

This address is mapped to the parameter Flow timeout (measured in

multiples of 0.86 seconds). This parameter controls how quickly the

stateful packet analysis can garbage-collect previous states. Smaller

values increase the number of concurrent flows that can be tracked. The

default value is 16.

Address 16

(Master FPGA)

This address is mapped to the parameter Flow length (measured in

packets). This parameter controls the maximum number of packets in a

flow that are considered for capturing. Typical values range from 6 to16.

Address 24

(PCI-X FPGA)

This address is mapped to the parameter Burst size (measured in 32-bit

words). This parameter sets the number of 32-bit words to transfer in one

PCI-X master cycle. Larger bursts achieve higher throughput but may

increase buffering latency and contention with other devices sharing the

same bus. The default value is 1024.

Address 36

(PCI-X FPGA)

This address specifies the count in PCI-X clocks before the DMA buffer is

transferred to the host if the buffer contains less than the programmed

burst size.