Watchdog timer, General, Wdt control status register (wcsr) – FANUC Robotics America V7865* User Manual

Page 67

67

Watchdog Timer

3

Watchdog Timer

General

The V7865 provides a programmable Watchdog Timer (WDT) which can be used to

reset the system if software integrity fails.

WDT Control Status Register (WCSR)

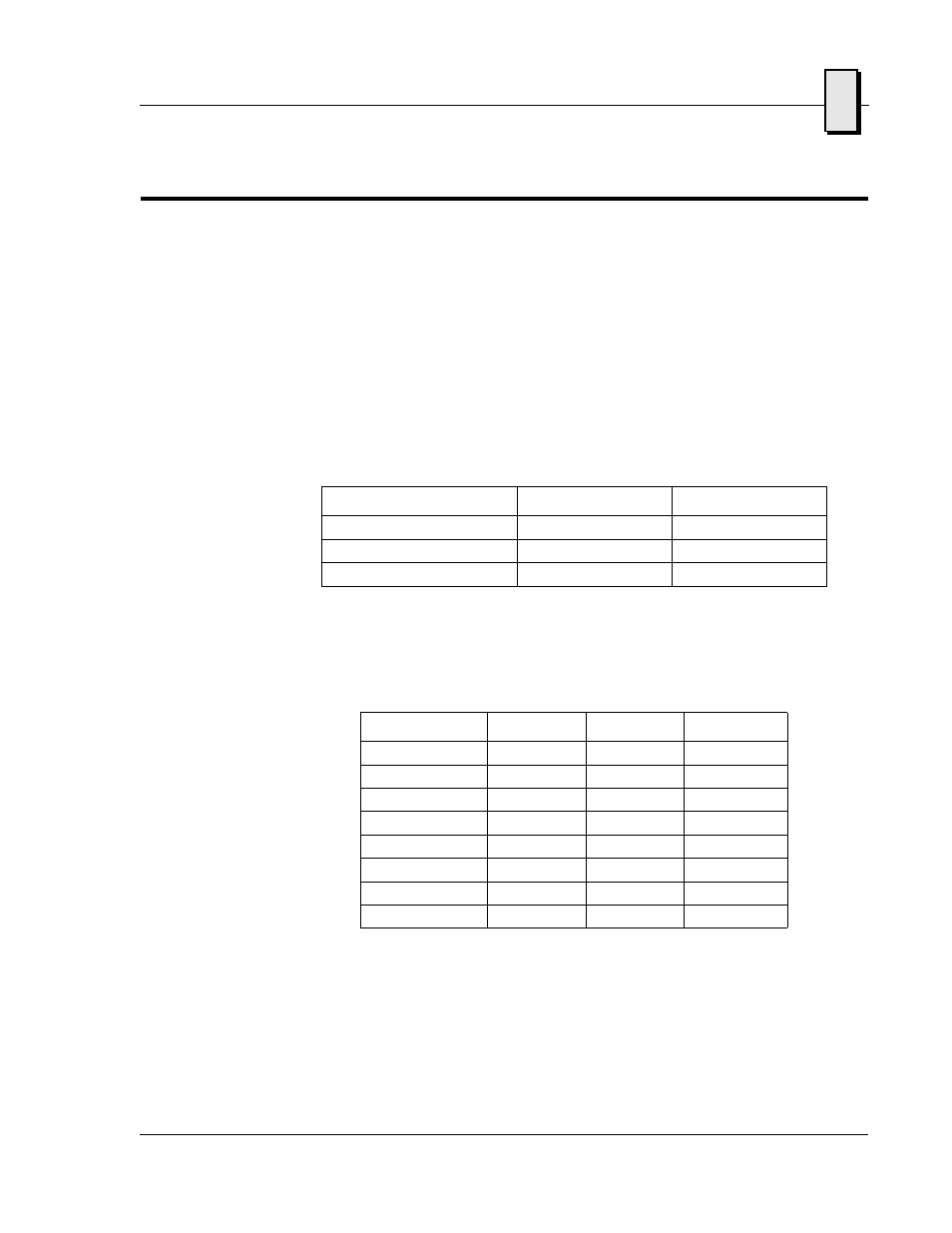

The WDT is controlled and monitored by the WDT Control Status Register (WCSR)

which is located at offset 0x08 from the address in BAR2. The mapping of the bits in

this register are as follows:

The “WDT Timeout Select” field is used to select the timeout value of the Watchdog

Timer as follows:

The “SERR/RST Select” bit is used to select whether the WDT generates an SERR# on

the local PCI bus or a system reset. If this bit is set to “0”, the WDT will generate a

system reset. Otherwise, the WDT will make the local PCI bus SERR# signal active.

Field

Bits

Read or Write

SERR/RST Select

WCSR[16]

Read/Write

WDT Timeout Select

WCSR[10..8]

Read/Write

WDT Enable

WCSR[0]

Read/Write

All of these bits default to “0” after system reset. All other bits are reserved.

Timeout

WCSR[10]

WCSR[9]

WCSR[8]

135s

0

0

0

33.6s

0

0

1

2.1s

0

1

0

524ms

0

1

1

262ms

1

0

0

131ms

1

0

1

32.768ms

1

1

0

2.048ms

1

1

1