Interrupts, System interrupts – FANUC Robotics America V7865* User Manual

Page 46

46

2

V7865 Product Manual

Interrupts

System Interrupts

In addition to an I/O port address, an I/O device has a separate hardware interrupt

line assignment. Assigned to each interrupt line is a corresponding interrupt vector in

the 256-vector interrupt table at $00000 to $003FF in memory. The 16 maskable

interrupts and the single Non-Maskable Interrupt (NMI) are listed in Table 2-3 along

with their functions. Table 2-4 on page 47 details the vectors in the interrupt vector

table. The interrupt number in HEX and decimal are also defined for real and

protected mode in Table 2-4 on page 47.

The interrupt hardware implementation on the V7865 is standard for computers built

around the PC architecture, which evolved from the IBM PC/XT. In the IBM PC/XT

computers, only eight interrupt request lines exist, numbered from IRQ0 to IRQ7 at

the PIC. The IBM PC/AT computer added eight more IRQx lines, numbered IRQ8 to

IRQ15, by cascading a second slave PIC into the original master PIC. IRQ2 at the

master PIC was committed as the cascade input from the slave PIC. This architecture

is represented in Figure 2-1 on page 51.

To maintain backward compatibility with PC/XT systems, IBM chose to use the new

IRQ9 input on the slave PIC to operate as the old IRQ2 interrupt line on the PC/XT

Expansion Bus. Thus, in AT systems, the IRQ9 interrupt line connects to the old IRQ2

pin (pin B4) on the AT Expansion Bus (or ISA bus).

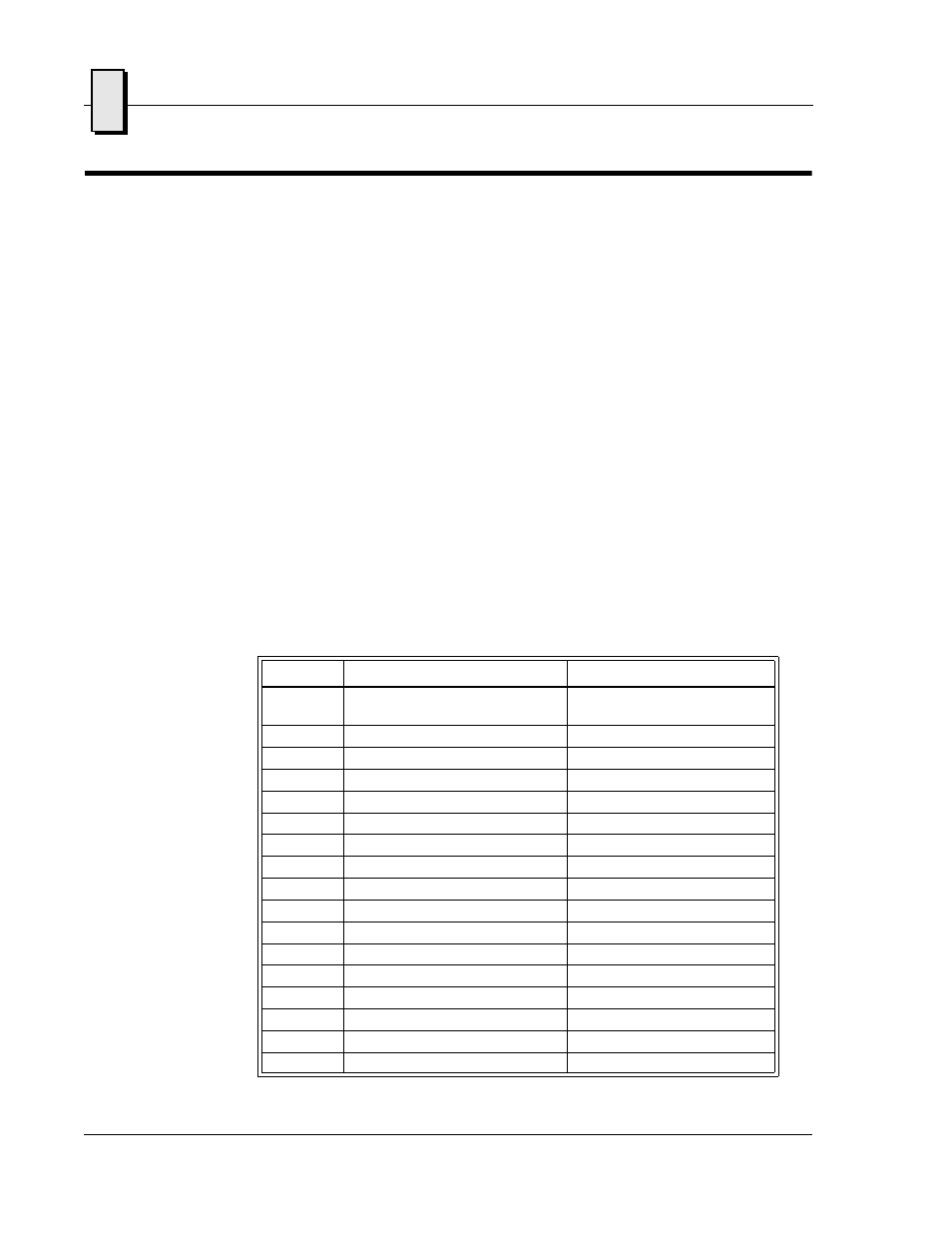

Table 2-3 Interrupt Line Assignments

IRQ

AT Function

Comments

NMI

Parity Errors

(Must be enabled in BIOS Setup)

Used by V7865 PCI bus

Interface

0

System Timer

Set by BIOS Setup

1

Keyboard

Set by BIOS Setup

2

Duplexed to IRQ9

3

COM2

4

COM1

5

Unused

6

Floppy Controller

7

Unused

8

Real-Time Clock

9

Old IRQ2

SVGA or Network I/O

10

Not Assigned

Determined by BIOS

11

Not Assigned

Determined by BIOS

12

Mouse

13

Math Coprocessor

14

AT Hard Drive

15

Flash Drive