Comtech EF Data DD2401 VME User Manual

Page 54

User Interfaces

DD2401 VME L-Band Demodulator Card Installation & Operational Manual

4-30

MN-VME2401 – Rev. B

<1>

<1>

<1>

<1>

<1>

<1>

<4>

<1>

<1>

<1>

<1>

<1>

<1>

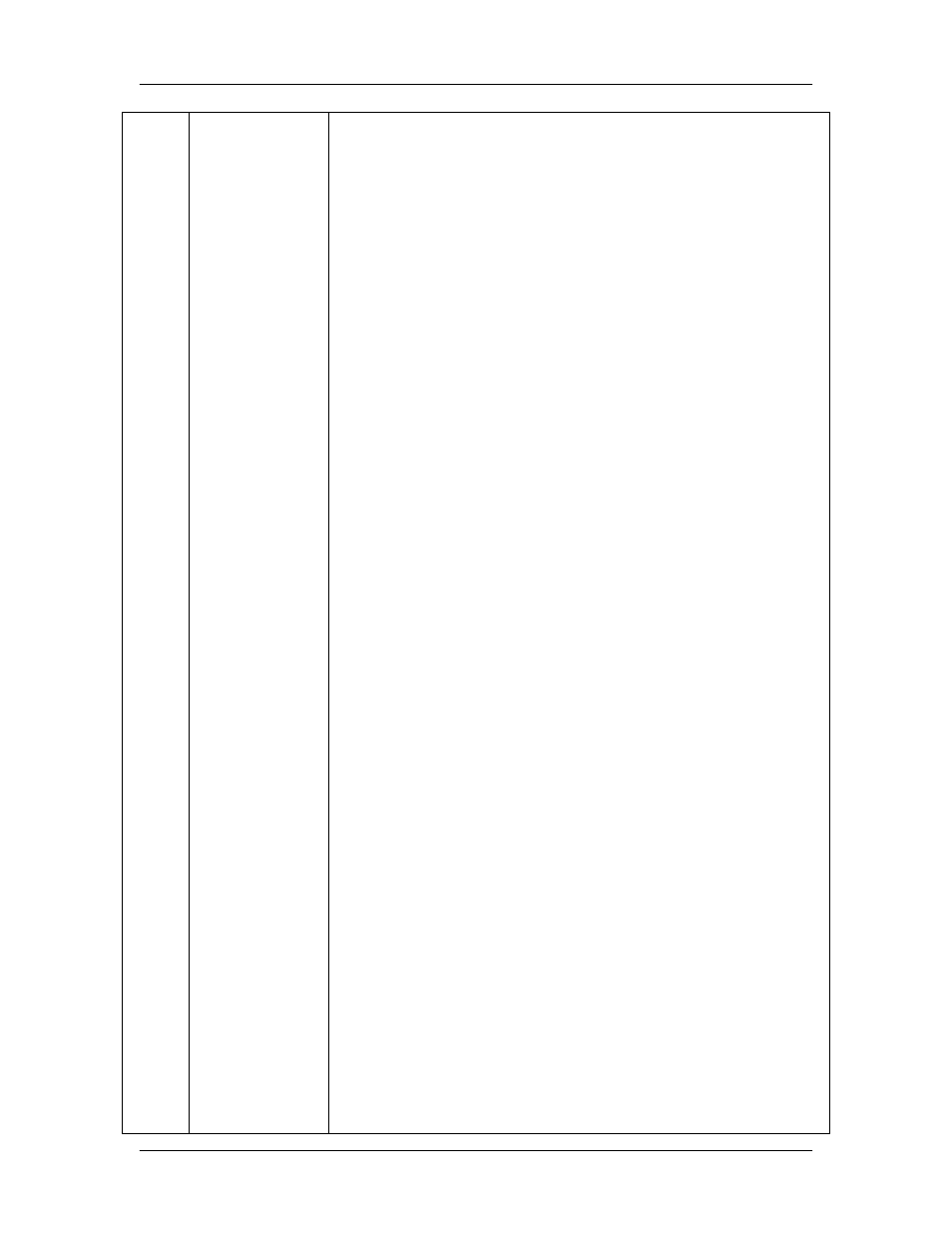

Reed-Solomon T

RS Interleaver

Depth

Differential

Decoder

Descrambler

Control

Descrambler

Type

Spectrum

Buffer Size

Buffer Clock

Buffer Clock

Polarity

Operating Mode

Alarm 1 Mask

Alarm 2 Mask

Alarm 3 Mask

Note: Always set to Zero; as the T value is calculated from N and

K.

Unsigned Binary, 4 or 8

0 = Off, 1 = On

0 = Disable, 1 = Enable

0 = None, 1 = IBS Scrambler, 2 = V35_IESS, 3 = V35_CCITT, 4 =

V35_EFDATA, 6 = OM73, 7 = Reed Solomon Scrambler, 8 =

V35_EFRS, 9 = TPC Scrambler

0 = Normal, 1 = Inverted

Byte 1 – 2 = Buffer Size in ms

Byte 3 - 4 = Buffer Size in Bytes

0 = External, 1 = Internal, 2 = EXC, 3 = RX SAT

0 = Normal, 1 = Inverted

0 = Normal, 1 = 2047 Test

Bit 0 = Receive Processor Fault

Bit 1 = Signal Lock Fault

Bit 2 = Receive Satellite AIS Fault

Bit 3 = Rx AGC Level Fault

Bit 4 = Reed-Solomon Sync Fault

Bit 5 = Reed-Solomon Excessive Errors Fault

Bit 6 = Reed-Solomon Uncorrectable Word Fault

Bit 7 = Receive Forced Alarm

(0 = Mask, 1 = Allow)

Bit 0 = Buffer Underflow

Bit 1 = Buffer Overflow

Bit 2 = Buffer Under 10%

Bit 3 = Buffer Over 90%

Bit 4 = Receive FPGA Configuration Fault

Bit 5 = Rx LNB Fault, LBST Only

Bit 6 - 7 = Spares

(0 = Mask, 1 = Allow)

Bit 0 = IF Synthesizer Lock Detect Fault

Bit 1 = Rx Oversample PLL Lock Detect Fault

Bit 2 = Buffer Clock PLL Lock Detect Fault

Bit 3 = Viterbi Decoder Lock Fault

Bit 4 = Sequential Decoder Lock Fault

Bit 5 = Rx 2047 Test Pattern Lock Fault

Bit 6 = External Reference PLL Lock Fault

Bit 7 = Frame Sync Fault

(0 = Mask, 1 = Allow)