Comtech EF Data DD2401 VME User Manual

Page 40

User Interfaces

DD2401 VME L-Band Demodulator Card Installation & Operational Manual

4-16

MN-VME2401 – Rev. B

<1>

<1>

<1>

<1>

<1>

<24>

<1>

<1>

*<1>

<1>

<1>

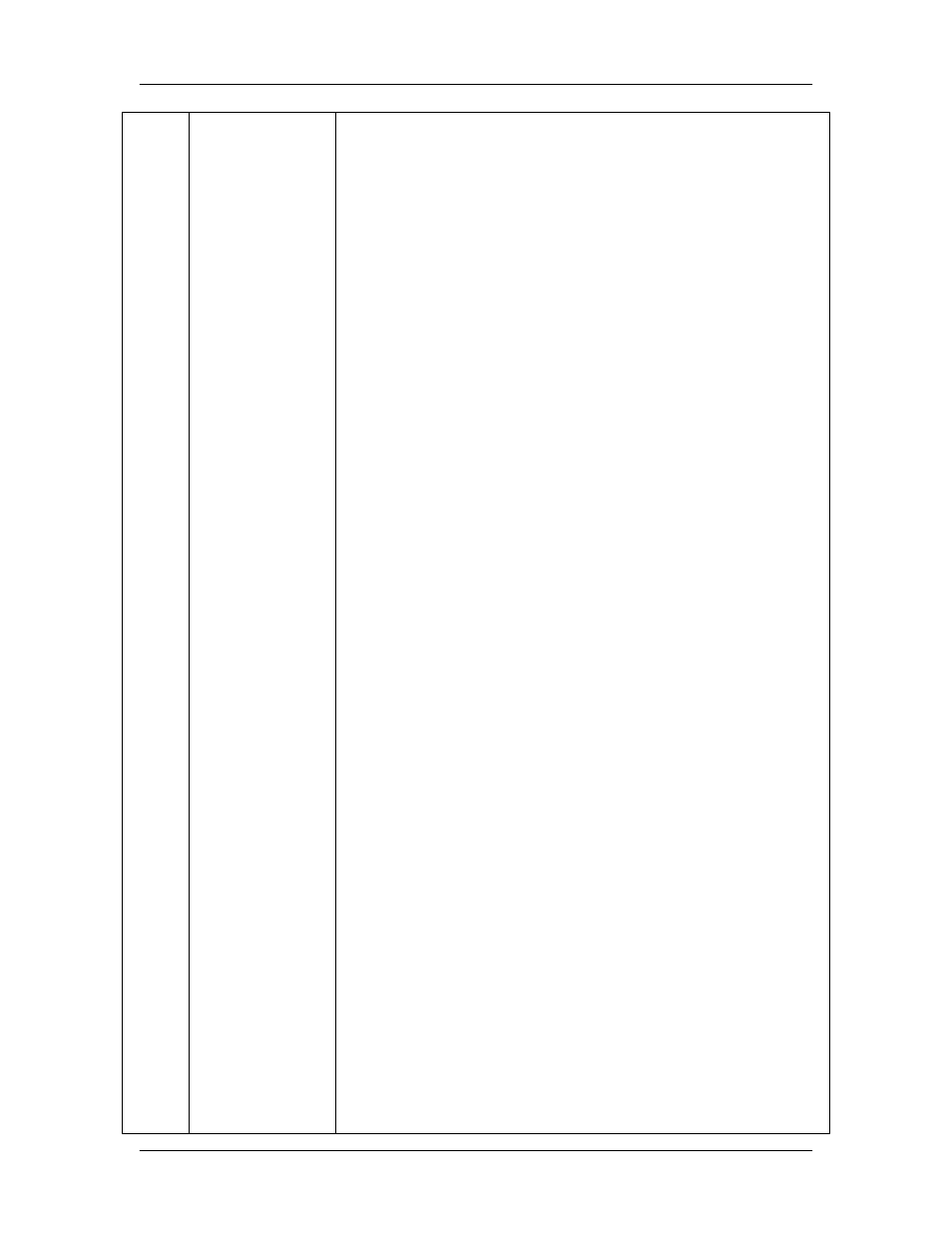

Alarm 3 Mask

Alarm 4 Mask

Common Alarm 1

Mask

Reserved

BER Measure

Period

Rx Circuit ID

Rx Terrestrial

Loopback

Rx Baseband

Loopback

Rx IF Loopback

Reserved

Data Invert

Bit 1 = Buffer Overflow

Bit 2 = Buffer Under 10%

Bit 3 = Buffer Over 90%

Bit 4 = Receive FPGA Configuration Alarm Fault

Bit 5 = Rx LNB Fault, LBST Only

Bits 6 - 7 = Spares

(0 = Mask, 1 = Allow)

Bit 0 = IF Synthesizer Lock Detect Fault

Bit 1 = Rx Oversample PLL Lock Detect Fault

Bit 2 = Buffer Clock PLL Lock Detect Fault

Bit 3 = Viterbi Decoder Lock Fault

Bit 4 = Sequential Decoder Lock Fault

Bit 5 = Rx 2047 Test Pattern Lock Fault

Bit 6 = External Reference PLL Lock Fault

Bit 7 = Frame Sync/Multiframe Sync Loss

(0 = Mask, 1 = Allow)

Bit 0 = Buffer Clock Activity Detect Fault

Bit 1 = External BNC Activity Detect Fault

Bit 2 = Rx Satellite Clock Activity Detect Fault

Bit 3 = External Reference PLL Activity Fault

Bit 4 = High Stability Activity Detect Fault

Bit 5 = High Stability PLL Fault

Bit 6 = Eb/No Threshold Fault

Bit 7 = Spare

(0 = Mask, 1 = Allow)

Bit 0 = -12 V Alarm

Bit 1 = +12 V Alarm

Bit 2 = +5 V Alarm

Bit 3 = Temperature

Bit 4 = Interface FPGA Fault

Bit 5 = Battery Fault

Bit 6 = RAM/ROM Fault

Bit 7 = Spare

(0 = Mask, 1 = Allow)

Set to Zero

Unsigned Binary Number of Bits in Measurement Period, in Powers

of Ten (ex: 6 = 10

6

Bits)

24 ASCII Characters

0 = Disabled, 1 = Enabled

0 = Disabled, 1 = Enabled

0 = Disabled, 1 = Enabled

Ignore

0 = Normal, 1 = Invert