Altera 100G Development Kit, Stratix V GX Edition User Manual

Page 18

2–10

Chapter 2: Board Components

Featured Device: Stratix V GX FPGA

100G Development Kit, Stratix V GX Edition

August 2012

Altera Corporation

Reference Manual

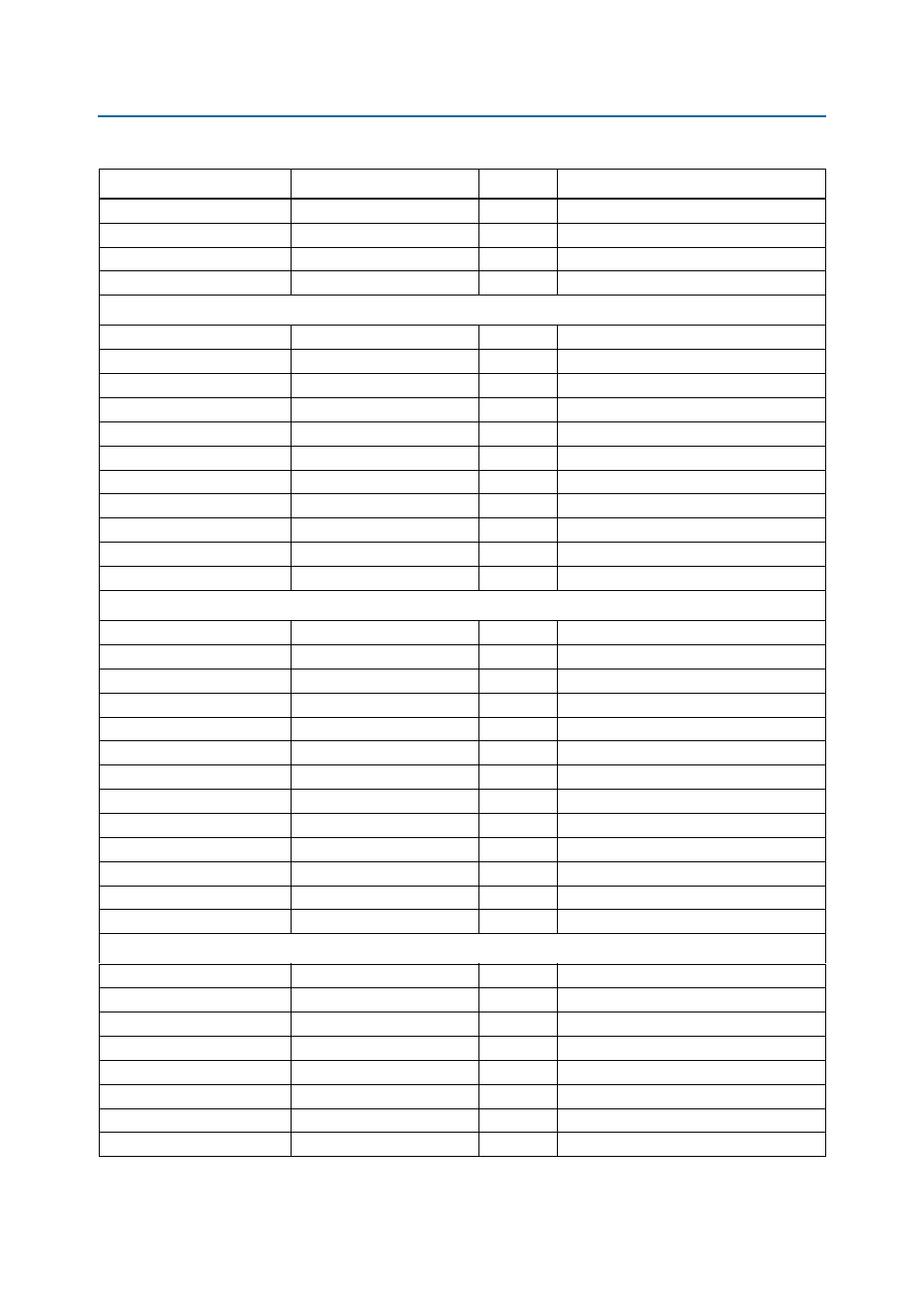

MAX2_CLK

2.5-V LVCMOS output

1

FPGA flash control

MAX2_OEN

2.5-V LVCMOS output

1

MAX II output enable

MAX2_WEN

2.5-V LVCMOS output

1

MAX II write enable

MAX2_CSN

2.5-V LVCMOS output

1

MAX II chip select

On-Board USB-Blaster II

USB_ADDR[1:0]

1.5-V output

2

USB-Blaster II address

USB_CLK

1.5-V output

1

USB-Blaster II clock

USB_DATA[7:0]

1.5-V bidirectional

8

USB-Blaster II data

USB_EMPTY

1.5-V input

1

USB-Blaster II empty

USB_FULL

1.5-V input

1

USB-Blaster II full

USB_OEN

1.5-V output

1

USB-Blaster II output enable

USB_RDN

1.5-V output

1

USB-Blaster II ready

USB_RESETN

1.5-V output

1

USB-Blaster II reset

USB_SCL

1.5-V output

1

USB-Blaster II two-wire clock

USB_SDA

1.5-V bidirectional

1

USB-Blaster II two-wire data

USB_WRN

1.5-V output

1

USB-Blaster II write enable

FPP Configuration

FPGA DCLK

2.5-V LVCMOS input

1

FPP clock

FPGA DATA[7:0]

2.5-V LVCMOS input

8

FPP data

FPGA_MSEL[4:0]

2.5-V LVCMOS input

5

Dedicated configuration pins

FPGA_CONFIGN

2.5-V LVCMOS

1

Dedicated configuration pins

FPGA_STATUSN

2.5-V LVCMOS output

1

Dedicated configuration pins

FPGA_CEN

2.5-V LVCMOS input

1

Dedicated configuration pins

FPGA_NIO_PULLUP

2.5-V LVCMOS input

1

Dedicated configuration pins

FPGA_CONF_DONE

2.5-V LVCMOS output

1

Dedicated configuration pins

FPGA_JTAG_TCK

2.5-V LVCMOS input

1

FPP JTAG chain clock

FPGA_JTAG_TDO

2.5-V LVCMOS

1

FPP JTAG chain data out

FPGA_JTAG_TMS

2.5-V LVCMOS input

1

FPP JTAG chain mode

FPGA_JTAG_TRST

2.5-V LVCMOS input

1

FPP JTAG chain reset

JTAG_BLASTER_TDO

2.5-V LVCMOS

1

MAX II CPLD on-board JTAG chain data out

User I/O

CPU_RESET

2.5-V LVCMOS input

1

Nios

®

II CPU reset push button

USER_RESET

2.5-V LVCMOS input

1

User reset push button

FPGA_USER_DIPSW[7:0]

2.5-V LVCMOS input

8

8 user DIP switches

FPGA_USER_LED[7:0]

2.5-V LVCMOS input

8

8 user LEDs

FPGA_USER_PB[3:0]

2.5-V LVCMOS input

4

4 user push buttons

LCD_CSN

2.5-V LVCMOS output

1

LCD chip select

LCD_D_CN

2.5-V LVCMOS output

1

LCD data or control signal

LCD_DATA[7:0]

2.5-V LVCMOS output

8

LCD data

Table 2–4. Stratix V GX I/O Usage Summary (Part 5 of 6)

Function

I/O Type

I/O Count

Description