Digilent 410-138P-KIT User Manual

Page 11

Genesys Reference Manual

www.digilentinc.com

page 11 of 28

Copyright Digilent, Inc. All rights reserved. Other product and company names mentioned may be trademarks of their respective owners

DDR2 SODIMM Pinout

Data

Address

Strobes Clk,Mask,I2C Control

DQ0: AF30 DQ16: AC28 DQ32: V29 DQ48: M28 AD0: L30

DS0P: AA29 CK0P: AK29 RAS#: H30

DQ1: AK31 DQ17: AB25 DQ33: Y27 DQ49: L28

AD1: M30 DS0N: AA30 CK0N: AJ29 CAS#: E31

DQ2: AF31 DQ18: AC27 DQ34: Y26 DQ50: F25

AD2: N29 DS1P: AK28 CK1P: E28

WE#: K29

DQ3: AD30 DQ19: AA26 DQ35: W24 DQ51: H25

AD3: P29 DS1N: AK27 CK1N: F28

BA0: G31

DQ4: AJ30 DQ20: AB26 DQ36: V28 DQ52: K27

AD4: K31 DS2P: AK26 CKE0: T28

BA1: J30

DQ5: AF29 DQ21: AA24 DQ37: W25 DQ53: K28

AD5: L31 DS2N: AJ27

CKE1: U30

BA2: R31

DQ6: AD29 DQ22: AB27 DQ38: W26 DQ54: H24

AD6: P31 DS3P: AB31

DM0: AJ31

S0: L29

DQ7: AE29 DQ23: AA25 DQ39: V24 DQ55: G26

AD7: P30 DS3N: AA31

DM1: AE28

S1: J29

DQ8: AH27 DQ24: AC29 DQ40: R24 DQ56: G25

AD8: M31 DS4P: Y28

DM2: Y24

ODT0: F31

DQ9: AF28 DQ25: AB30 DQ41: P25 DQ57: M26 AD9: R28 DS4N: Y29

DM3: Y31

ODT1: F30

DQ10: AH28 DQ26: W31

DQ42: N24 DQ58: J24 AD10: J31

DS5P: E26

DM4: V25

DQ11: AA28 DQ27: V30

DQ43: P26 DQ59: L26 AD11: R29 DS5N: E27

DM5: P24

DQ12: AG25 DQ28: AC30 DQ44: T24 DQ60: J27 AD12: T31 DS6P: H28

DM6: F26

DQ13: AJ26 DQ29: W29

DQ45: N25 DQ61: M25 AD13: H29 DS6N: G28

DM7: J25

DQ14: AG28 DQ30: V27

DQ46: P27 DQ62: L25

DS7P: G27

SDA: F29

DQ15: AB28 DQ31: W27

DQ47: N28 DQ63: L24

DS7N: H27

SCK: E29

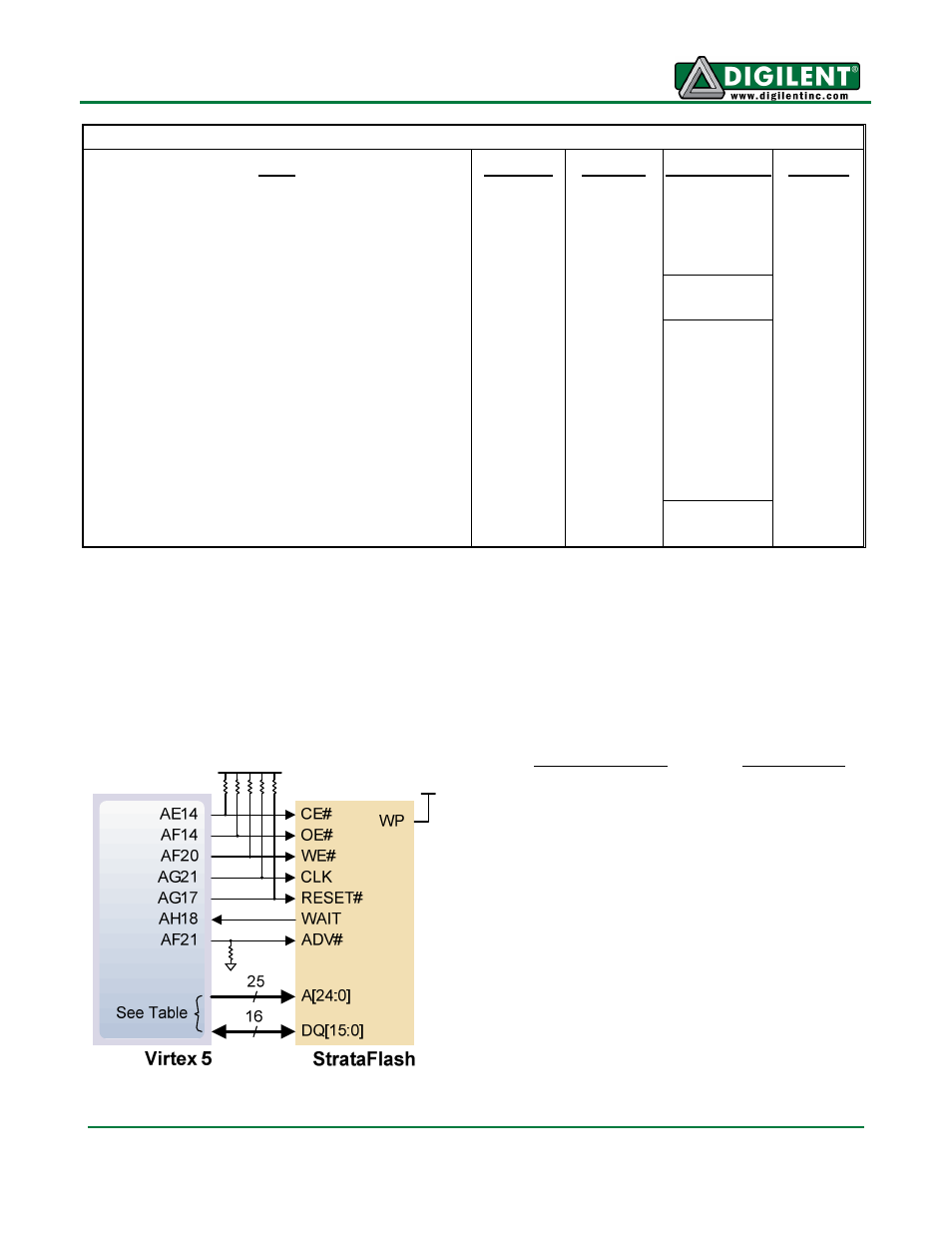

Flash Memory

The Genesys board uses a 256Mbit Numonyx P30 parallel flash memory device (organized as 16-bit

by 16Mbytes) for non-volatile storage of FPGA configuration files. Configuration files are stored using

the byte-peripheral interface mode (BPI) in either up or down configurations. A single FPGA

configuration file requires less than 16Mbits, leaving 140Mbits available for user data. Data can be

transferred to/from the Flash by user applications, or by facilities built into the Adept software. A

reference design on the Digilent website provides an example of driving the Flash memory.

Address Signals

Data Signals

A0: K12

A13: K16

D0: AD19

A1: K13

A14: K21

D1: AE19

A2: H23

A15: J22

D2: AE17

A3: G23

A16: L16

D3: AF16

A4: H12

A17: L15

D4: AD20

A5: J12

A18: L20

D5: AE21

A6: K22

A19: L21

D6: AE16

A7: K23

A20: AE23

D7: AF15

A8: K14

A21: AE22

D8: AH13

A9: L14

A22: AG12

D9: AH14

A10: H22

A23: AF13

D10: AH19

A11: G22

A24: AG23

D11: AH20

A12: J15

D12: AG13

D13: AH12

D14: AH22

D15: AG22