Cypress Perform CY7C68013 User Manual

Page 61

CY7C68013A, CY7C68014A

CY7C68015A, CY7C68016A

Document #: 38-08032 Rev. *L

Page 61 of 62

Document History Page

Document Title: CY7C68013A, CY7C68014A, CY7C68015A, CY7C68016A, EZ-USB FX2LP™ USB Microcontroller

High-Speed USB Peripheral Controller

Document Number: 38-08032

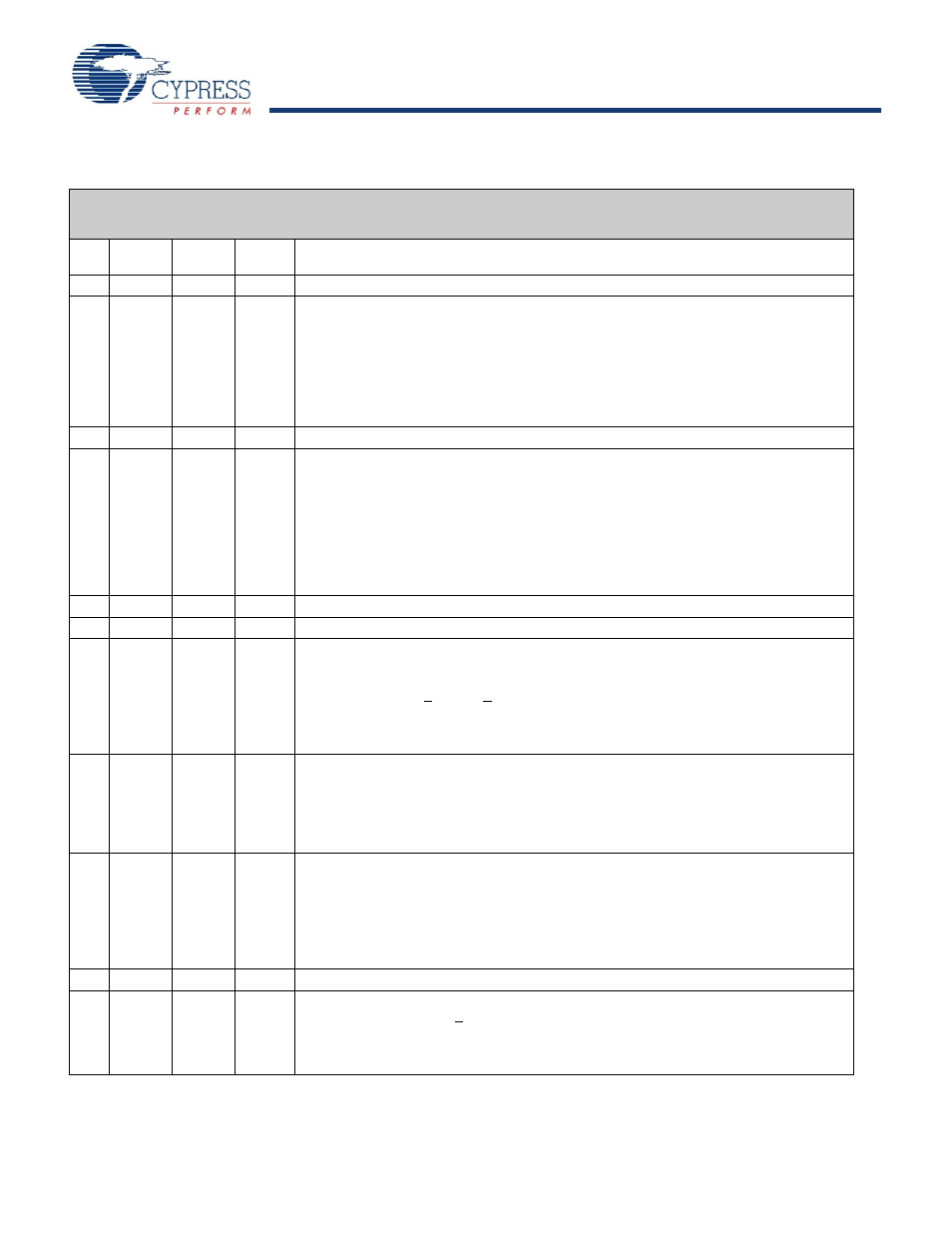

REV. ECN NO.

Issue

Date

Orig. of

Change

Description of Change

**

124316 03/17/03

VCS

New data sheet

*A

128461 09/02/03

VCS

Added PN CY7C68015A throughout data sheet

Modified

to add ECC block and fix errors

Removed word “compatible” where associated with I

2

C

Corrected grammar and formatting in various locations

Updated Sections 3.2.1, 3.9, 3.11,

, Section 5.0

Added Sections 3.15, 3.18.4, 3.20

Modified

Updated

to match current spec revision

*B

130335 10/09/03

KKV

Restored PRELIMINARY to header (had been removed in error from rev. *A)

*C

131673 02/12/04

KKU

Section 8.1 changed “certified” to “compliant”

added parameter V

IH_X

and V

IL_X

Added Sequence diagrams Section 9.16

Updated Ordering information with lead-free parts

Updated Registry Summary

Section 3.12.4:example changed to column 8 from column 9

Updated

memory write timing Diagram

Updated section 3.9 (reset)

Updated section 3.15 ECC Generation

*D

230713 See ECN

KKU

Changed Lead free Marketing part numbers in

as per spec change in 28-00054.

*E

242398 See ECN

TMD

Minor Change: data sheet posted to the web,

*F

271169 See ECN

MON

Added USB-IF Test ID number

Added USB 2.0 logo

Added values for Isusp, Icc, Power Dissipation, Vih_x, Vil_x

Changed VCC from + 10% to + 5%

Changed E-Pad size to 4.3 mm x 5.0 mm

Changed PKTEND to FLAGS output propagation delay (asynchronous interface) in

from a max value of 70 ns to 115 ns

*G

316313 See ECN

MON

Removed CY7C68013A-56PVXCT part availability

Added parts ideal for battery powered applications: CY7C68014A, CY7C68016A

Provided additional timing restrictions and requirement about the use of PKETEND pin to

commit a short one byte/word packet subsequent to committing a packet automatically

(when in auto mode).

Added Min Vcc Ramp Up time (0 to 3.3v)

*H

338901 See ECN

MON

Added information about the AUTOPTR1/AUTOPTR2 address timing with regards to data

memory read/write timing diagram.

Removed TBD for Min value of Clock to FIFO Data Output Propagation Delay (t

XFD

) for

Slave FIFO Synchronous Read

Changed

to include part CY7C68016A-56LFXC in the part listed for battery

powered applications

Added register GPCR2 in register summary

*I

371097 See ECN

MON

Added timing for strobing RD#/WR# signals when using PortC strobe feature (Section 10.5)

*J

397239 See ECN

MON

Removed XTALINSRC register from register summary.

Changed Vcc margins to +10%

Added 56-pin VFBGA Pin Package Diagram

Added 56-pin VFBGA definition in pin listing

Added RDK part number to the Ordering Information table