9 reset and wakeup, 1 reset pin – Cypress Perform CY7C68013 User Manual

Page 6

CY7C68013A, CY7C68014A

CY7C68015A, CY7C68016A

Document #: 38-08032 Rev. *L

Page 6 of 62

If Autovectoring is enabled (AV4EN = 1 in the INTSET-UP

register), the FX 2LP substitutes its INT4VEC byte. Therefore, if

the high byte (“page”) of a jump-table address is preloaded at

location 0x0054, the automatically inserted INT4VEC byte at

0x0055 directs the jump to the correct address out of the 14

addresses within the page. When the ISR occurs, the FX2LP

pushes the program counter onto its stack then jumps to address

0x0053, where it expects to find a “jump” instruction to the ISR

Interrupt service routine.

3.9 Reset and Wakeup

3.9.1 Reset Pin

The input pin, RESET#, resets the FX2LP when asserted. This

pin has hysteresis and is active LOW. When a crystal is used with

the CY7C680xxA the reset period must allow for the stabilization

of the crystal and the PLL. This reset period must be approxi-

mately 5 ms after VCC reaches 3.0V. If the crystal input pin is

driven by a clock signal the internal PLL stabilizes in 200

μs after

VCC has reached 3.0V.

on page 7 shows a power on reset condition and a reset

applied during operation. A power on reset is defined as the time

reset that is asserted while power is being applied to the circuit.

A powered reset is when the FX2LP powered on and operating

and the RESET# pin is asserted.

Cypress provides an application note which describes and

recommends power on reset implementation. For more infor-

mation about reset implementation for the FX2 family of products

visit

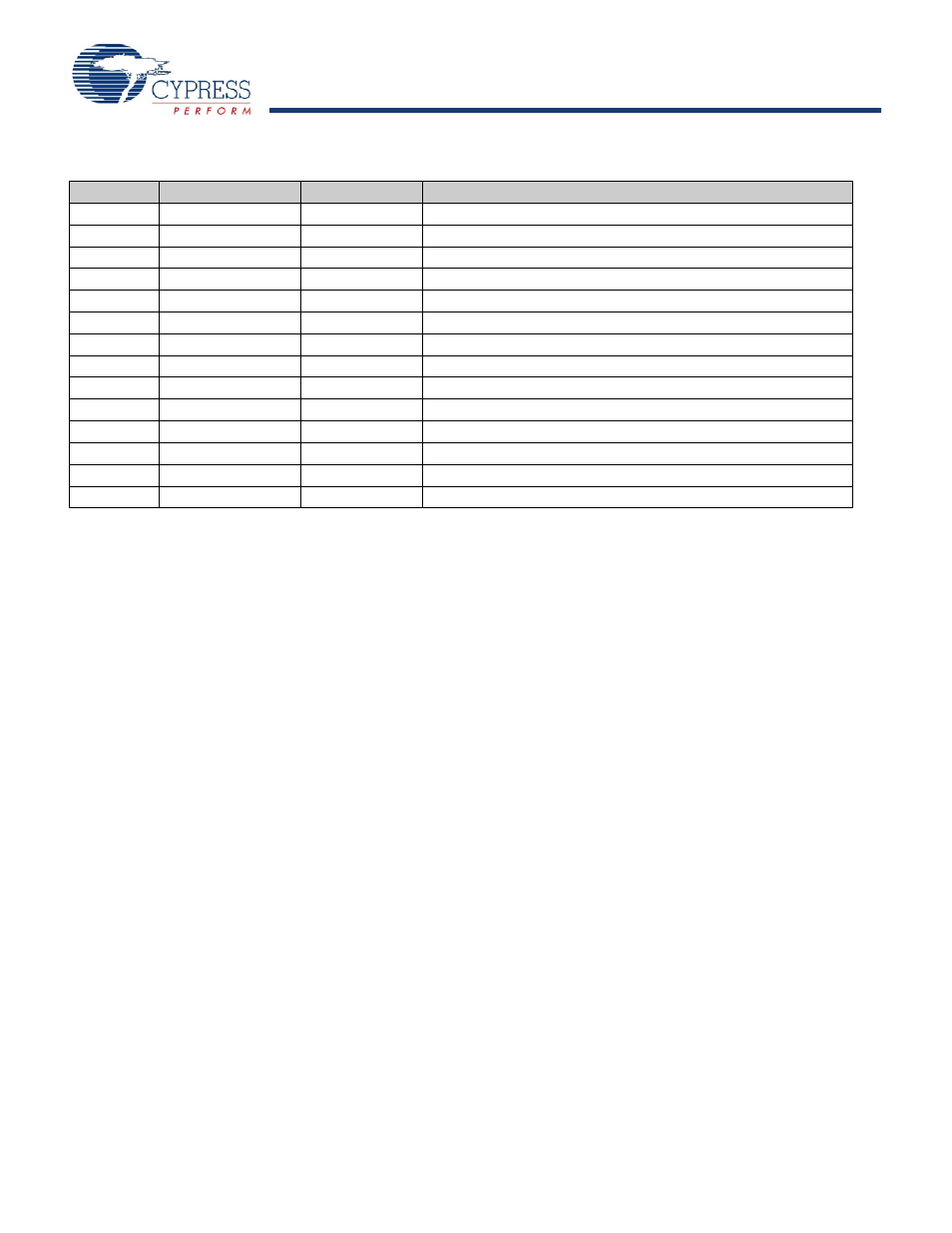

Table 4. Individual FIFO/GPIF Interrupt Sources

Priority

INT4VEC Value

Source

Notes

1

80

EP2PF

Endpoint 2 Programmable Flag

2

84

EP4PF

Endpoint 4 Programmable Flag

3

88

EP6PF

Endpoint 6 Programmable Flag

4

8C

EP8PF

Endpoint 8 Programmable Flag

5

90

EP2EF

Endpoint 2 Empty Flag

6

94

EP4EF

Endpoint 4 Empty Flag

7

98

EP6EF

Endpoint 6 Empty Flag

8

9C

EP8EF

Endpoint 8 Empty Flag

9

A0

EP2FF

Endpoint 2 Full Flag

10

A4

EP4FF

Endpoint 4 Full Flag

11

A8

EP6FF

Endpoint 6 Full Flag

12

AC

EP8FF

Endpoint 8 Full Flag

13

B0

GPIFDONE

GPIF Operation Complete

14

B4

GPIFWF

GPIF Waveform

Note

3. If the external clock is powered at the same time as the CY7C680xxA and has a stabilization wait period, it must be added to the 200

μs.