Cypress CY7C1462AV33 User Manual

Features, Functional description

36-Mbit (1M x 36/2M x 18/512K x 72)

Pipelined SRAM with NoBL™ Architecture

CY7C1460AV33

CY7C1462AV33

CY7C1464AV33

Cypress Semiconductor Corporation

•

198 Champion Court

•

San Jose

,

CA 95134-1709

•

408-943-2600

Document #: 38-05353 Rev. *D

Revised June 22, 2006

Features

• Pin-compatible and functionally equivalent to ZBT™

• Supports 250-MHz bus operations with zero wait states

— Available speed grades are 250, 200 and 167 MHz

• Internally self-timed output buffer control to eliminate

the need to use asynchronous OE

• Fully registered (inputs and outputs) for pipelined

operation

• Byte Write capability

• 3.3V power supply

• 3.3V/2.5V I/O power supply

• Fast clock-to-output times

— 2.6 ns (for 250-MHz device)

• Clock Enable (CEN) pin to suspend operation

• Synchronous self-timed writes

• CY7C1460AV33, CY7C1462AV33 available in

JEDEC-standard lead-free 100-pin TQFP, lead-free and

non-lead-free 165-ball FBGA package. CY7C1464AV33

available in lead-free and non-lead-free 209-ball FBGA

package

• IEEE 1149.1 JTAG-Compatible Boundary Scan

• Burst capability—linear or interleaved burst order

• “ZZ” Sleep Mode option and Stop Clock option

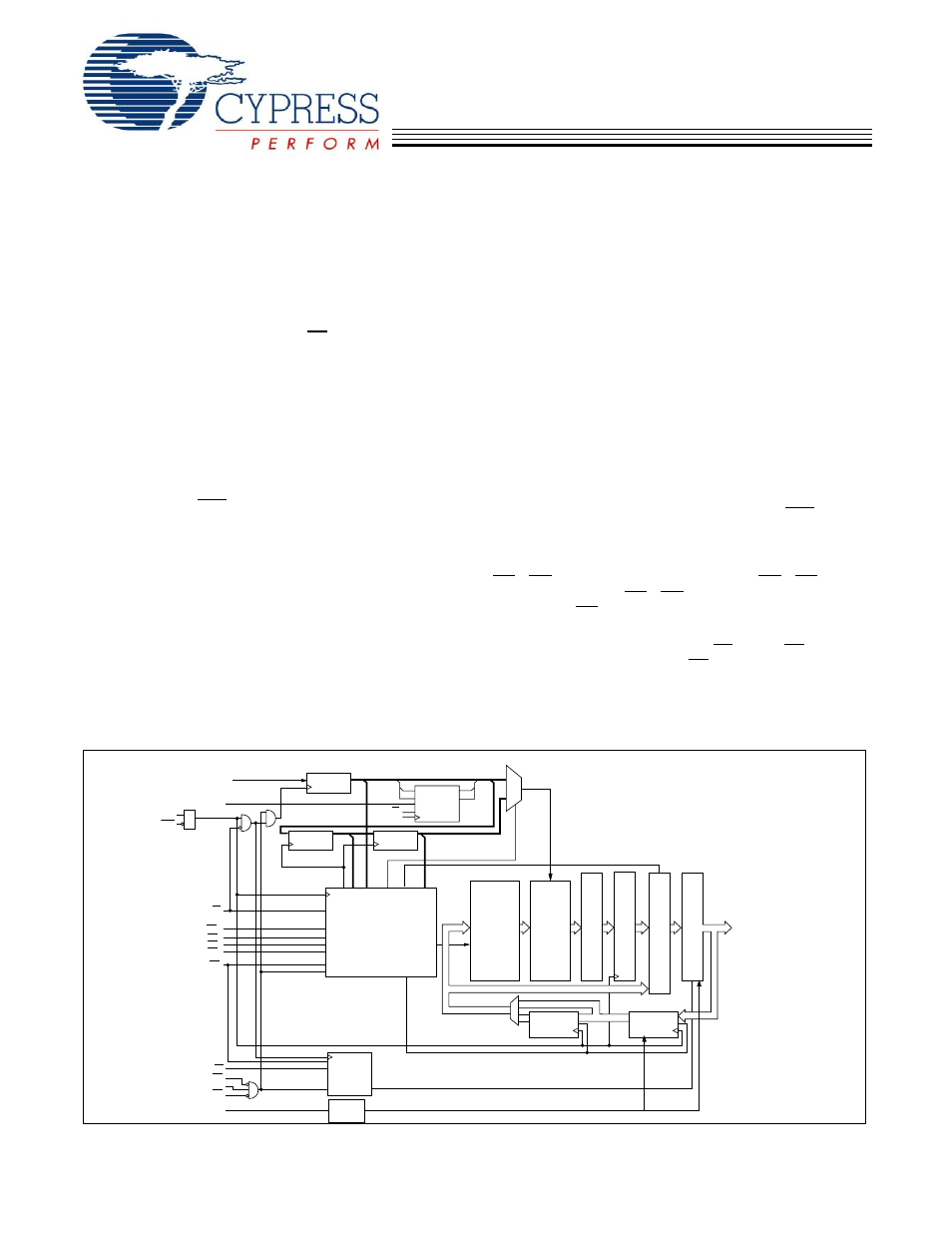

Functional Description

The CY7C1460AV33/CY7C1462AV33/CY7C1464AV33 are

3.3V, 1M x 36/2M x 18/512K x72 Synchronous pipelined burst

SRAMs with No Bus Latency™ (NoBL

™) logic, respectively.

They are designed to support unlimited true back-to-back

Read/Write operations with no wait states. The

CY7C1460AV33/CY7C1462AV33/CY7C1464AV33 are

equipped with the advanced (NoBL) logic required to enable

consecutive Read/Write operations with data being trans-

ferred on every clock cycle. This feature dramatically improves

the throughput of data in systems that require frequent

Write/Read transitions. The

CY7C1460AV33/CY7C1462AV33/CY7C1464AV33 are pin

compatible and functionally equivalent to ZBT devices.

All synchronous inputs pass through input registers controlled

by the rising edge of the clock. All data outputs pass through

output registers controlled by the rising edge of the clock. The

clock input is qualified by the Clock Enable (CEN) signal,

which when deasserted suspends operation and extends the

previous clock cycle.

Write operations are controlled by the Byte Write Selects

(BW

a

–BW

h

for CY7C1464AV33, BW

a

–BW

d

for

CY7C1460AV33 and BW

a

–BW

b

for CY7C1462AV33) and a

Write Enable (WE) input. All writes are conducted with on-chip

synchronous self-timed write circuitry.

Three synchronous Chip Enables (CE

1

, CE

2

, CE

3

) and an

asynchronous Output Enable (OE) provide for easy bank

selection and output tri-state control. In order to avoid bus

contention, the output drivers are synchronously tri-stated

during the data portion of a write sequence.

A0, A1, A

C

MODE

BW

a

BW

b

WE

CE1

CE2

CE3

OE

READ LOGIC

DQs

DQP

a

DQP

b

DQP

c

DQP

d

D

A

T

A

S

T

E

E

R

I

N

G

O

U

T

P

U

T

B

U

F

F

E

R

S

MEMORY

ARRAY

E

E

INPUT

REGISTER 0

ADDRESS

REGISTER 0

WRITE ADDRESS

REGISTER 1

WRITE ADDRESS

REGISTER 2

WRITE REGISTRY

AND DATA COHERENCY

CONTROL LOGIC

BURST

LOGIC

A0'

A1'

D1

D0

Q1

Q0

A0

A1

C

ADV/LD

ADV/LD

E

INPUT

REGISTER 1

S

E

N

S

E

A

M

P

S

E

CLK

CEN

WRITE

DRIVERS

BW

c

BW

d

ZZ

SLEEP

CONTROL

O

U

T

P

U

T

R

E

G

I

S

T

E

R

S

Logic Block Diagram-CY7C1460AV33 (1M x 36)