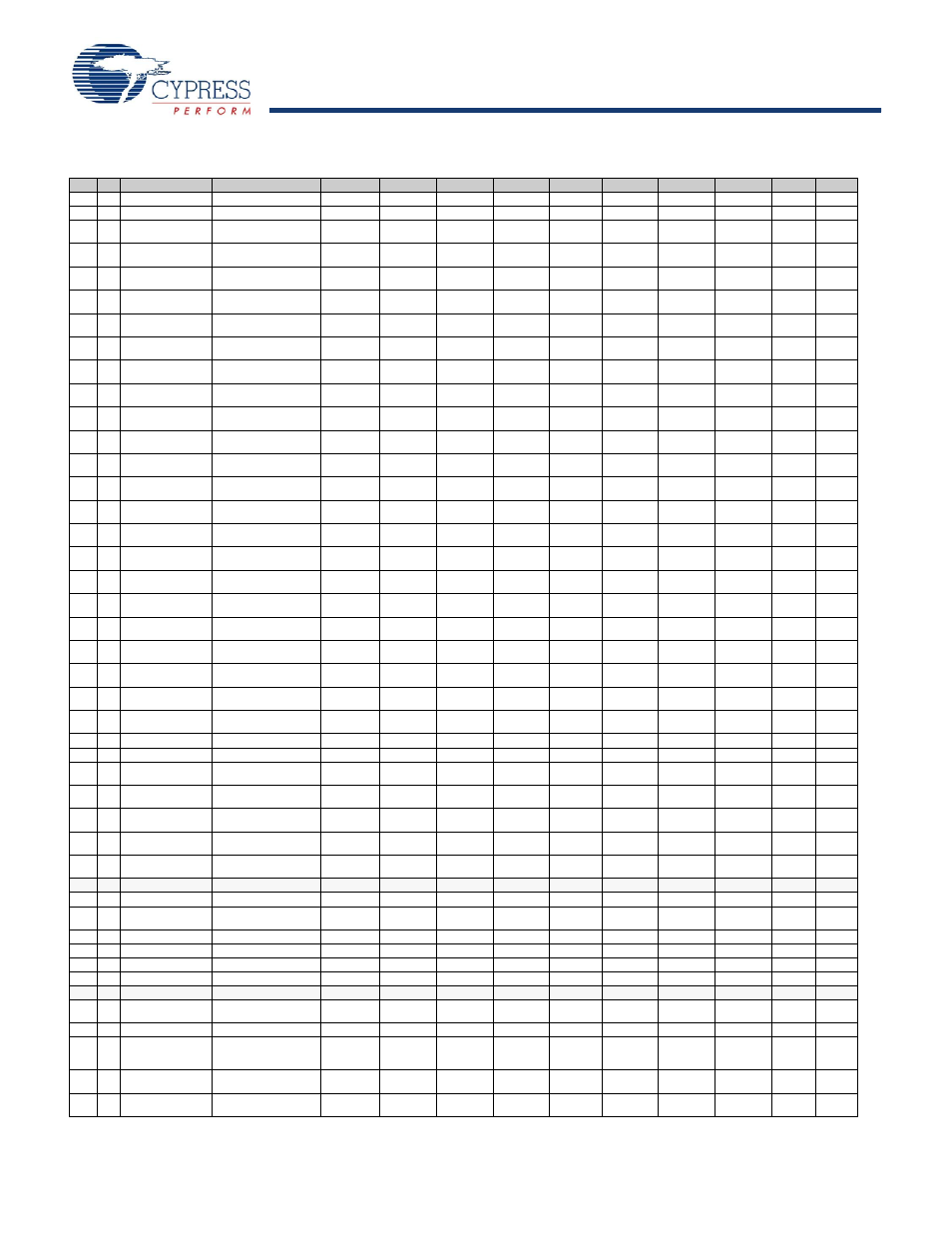

Table 12. fx2lp register summary (continued) – Cypress Perform CY7C68013 User Manual

Page 32

CY7C68013A, CY7C68014A

CY7C68015A, CY7C68016A

Document #: 38-08032 Rev. *L

Page 32 of 62

E69D 1

EP8BCL

Endpoint 8 Byte Count L BC7/SKIP

BC6

BC5

BC4

BC3

BC2

BC1

BC0

xxxxxxxx RW

E69E 2

reserved

E6A0 1

EP0CS

Endpoint 0 Control and

Status

HSNAK

0

0

0

0

0

BUSY

STALL

10000000 bbbbbbrb

E6A1 1

EP1OUTCS

Endpoint 1 OUT Control

and Status

0

0

0

0

0

0

BUSY

STALL

00000000 bbbbbbrb

E6A2 1

EP1INCS

Endpoint 1 IN Control and

Status

0

0

0

0

0

0

BUSY

STALL

00000000 bbbbbbrb

E6A3 1

EP2CS

Endpoint 2 Control and

Status

0

NPAK2

NPAK1

NPAK0

FULL

EMPTY

0

STALL

00101000 rrrrrrrb

E6A4 1

EP4CS

Endpoint 4 Control and

Status

0

0

NPAK1

NPAK0

FULL

EMPTY

0

STALL

00101000 rrrrrrrb

E6A5 1

EP6CS

Endpoint 6 Control and

Status

0

NPAK2

NPAK1

NPAK0

FULL

EMPTY

0

STALL

00000100 rrrrrrrb

E6A6 1

EP8CS

Endpoint 8 Control and

Status

0

0

NPAK1

NPAK0

FULL

EMPTY

0

STALL

00000100 rrrrrrrb

E6A7 1

EP2FIFOFLGS

Endpoint 2 slave FIFO

Flags

0

0

0

0

0

PF

EF

FF

00000010 R

E6A8 1

EP4FIFOFLGS

Endpoint 4 slave FIFO

Flags

0

0

0

0

0

PF

EF

FF

00000010 R

E6A9 1

EP6FIFOFLGS

Endpoint 6 slave FIFO

Flags

0

0

0

0

0

PF

EF

FF

00000110 R

E6AA 1

EP8FIFOFLGS

Endpoint 8 slave FIFO

Flags

0

0

0

0

0

PF

EF

FF

00000110 R

E6AB 1

EP2FIFOBCH

Endpoint 2 slave FIFO

total byte count H

0

0

0

BC12

BC11

BC10

BC9

BC8

00000000 R

E6AC 1

EP2FIFOBCL

Endpoint 2 slave FIFO

total byte count L

BC7

BC6

BC5

BC4

BC3

BC2

BC1

BC0

00000000 R

E6AD 1

EP4FIFOBCH

Endpoint 4 slave FIFO

total byte count H

0

0

0

0

0

BC10

BC9

BC8

00000000 R

E6AE 1

EP4FIFOBCL

Endpoint 4 slave FIFO

total byte count L

BC7

BC6

BC5

BC4

BC3

BC2

BC1

BC0

00000000 R

E6AF 1

EP6FIFOBCH

Endpoint 6 slave FIFO

total byte count H

0

0

0

0

BC11

BC10

BC9

BC8

00000000 R

E6B0 1

EP6FIFOBCL

Endpoint 6 slave FIFO

total byte count L

BC7

BC6

BC5

BC4

BC3

BC2

BC1

BC0

00000000 R

E6B1 1

EP8FIFOBCH

Endpoint 8 slave FIFO

total byte count H

0

0

0

0

0

BC10

BC9

BC8

00000000 R

E6B2 1

EP8FIFOBCL

Endpoint 8 slave FIFO

total byte count L

BC7

BC6

BC5

BC4

BC3

BC2

BC1

BC0

00000000 R

E6B3 1

SUDPTRH

Setup Data Pointer high

address byte

A15

A14

A13

A12

A11

A10

A9

A8

xxxxxxxx RW

E6B4 1

SUDPTRL

Setup Data Pointer low ad-

dress byte

A7

A6

A5

A4

A3

A2

A1

0

xxxxxxx0 bbbbbbbr

E6B5 1

SUDPTRCTL

Setup Data Pointer Auto

Mode

0

0

0

0

0

0

0

SDPAUTO

00000001 RW

2

reserved

E6B8 8

SET-UPDAT

8 bytes of setup data

D7

D6

D5

D4

D3

D2

D1

D0

xxxxxxxx R

SET-UPDAT[0] =

bmRequestType

SET-UPDAT[1] =

bmRequest

SET-UPDAT[2:3] = wVal-

ue

SET-UPDAT[4:5] = wInd-

ex

SET-UPDAT[6:7] =

wLength

GPIF

E6C0 1

GPIFWFSELECT

Waveform Selector

SINGLEWR1 SINGLEWR0 SINGLERD1 SINGLERD0 FIFOWR1

FIFOWR0

FIFORD1

FIFORD0

11100100 RW

E6C1 1

GPIFIDLECS

GPIF Done, GPIF IDLE

drive mode

DONE

0

0

0

0

0

0

IDLEDRV

10000000 RW

E6C2 1

GPIFIDLECTL

Inactive Bus, CTL states 0

0

CTL5

CTL4

CTL3

CTL2

CTL1

CTL0

11111111 RW

E6C3 1

GPIFCTLCFG

CTL Drive Type

TRICTL

0

CTL5

CTL4

CTL3

CTL2

CTL1

CTL0

00000000 RW

E6C4 1

GPIFADRH

GPIF Address H

0

0

0

0

0

0

0

GPIFA8

00000000 RW

E6C5 1

GPIFADRL

[11]

GPIF Address L

GPIFA7

GPIFA6

GPIFA5

GPIFA4

GPIFA3

GPIFA2

GPIFA1

GPIFA0

00000000 RW

FLOWSTATE

E6C6 1

FLOWSTATE

Flowstate Enable and

Selector

FSE

0

0

0

0

FS2

FS1

FS0

00000000 brrrrbbb

E6C7 1

FLOWLOGIC

Flowstate Logic

LFUNC1

LFUNC0

TERMA2

TERMA1

TERMA0

TERMB2

TERMB1

TERMB0

00000000 RW

E6C8 1

FLOWEQ0CTL

CTL-Pin States in

Flowstate

(when Logic = 0)

CTL0E3

CTL0E2

CTL0E1/

CTL5

CTL0E0/

CTL4

CTL3

CTL2

CTL1

CTL0

00000000 RW

E6C9 1

FLOWEQ1CTL

CTL-Pin States in Flow-

state (when Logic = 1)

CTL0E3

CTL0E2

CTL0E1/

CTL5

CTL0E0/

CTL4

CTL3

CTL2

CTL1

CTL0

00000000 RW

E6CA 1

FLOWHOLDOFF

Holdoff Configuration

HOPERIOD3 HOPERIOD2 HOPERIOD1 HOPERIOD

0

HOSTATE

HOCTL2

HOCTL1

HOCTL0

00010010 RW

Table 12. FX2LP Register Summary (continued)

Hex

Size Name

Description

b7

b6

b5

b4

b3

b2

b1

b0

Default

Access