1 cy7c68013a/15a pin descriptions – Cypress Perform CY7C68013 User Manual

Page 21

CY7C68013A, CY7C68014A

CY7C68015A, CY7C68016A

Document #: 38-08032 Rev. *L

Page 21 of 62

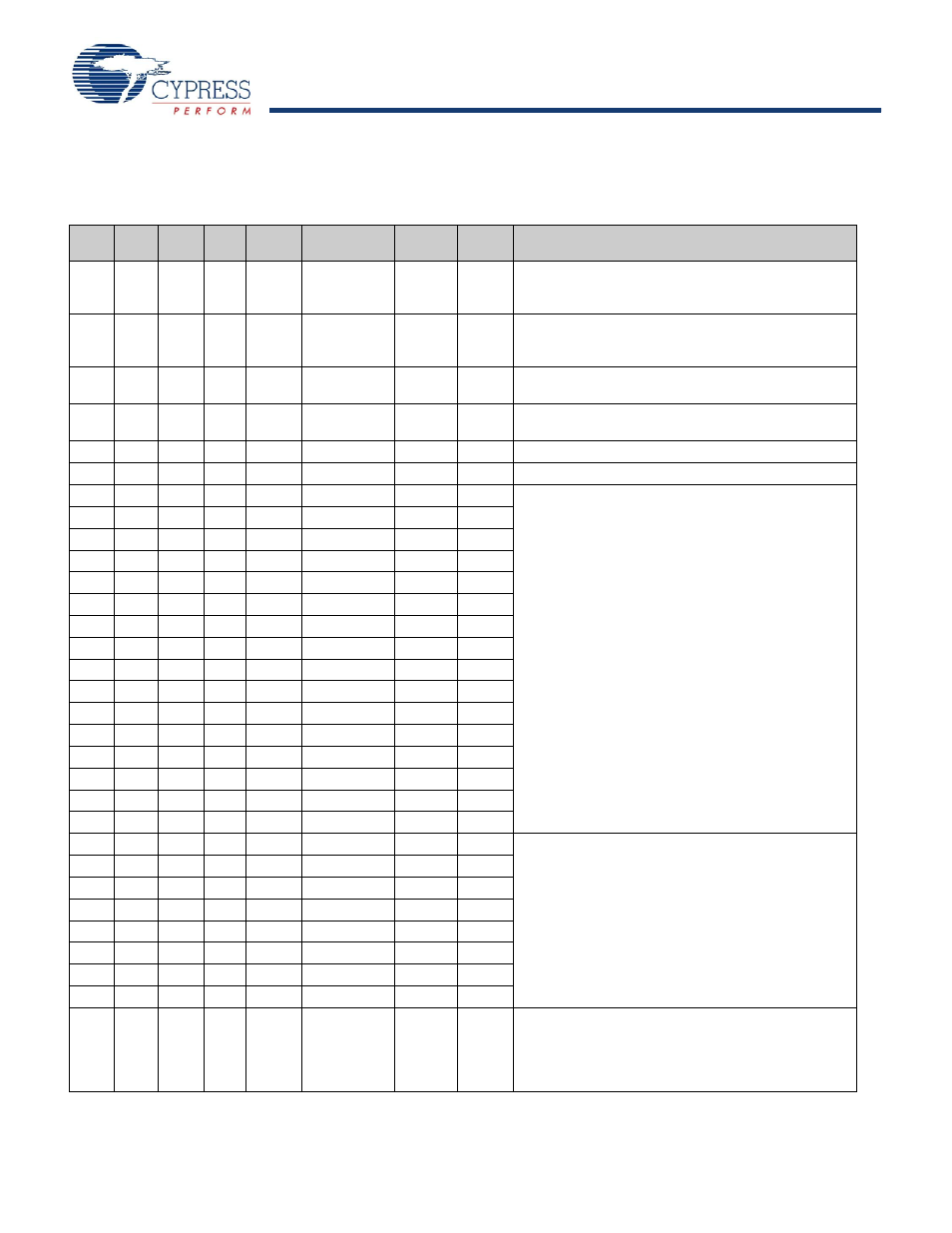

4.1 CY7C68013A/15A Pin Descriptions

The FX2LP Pin Descriptions follows.

Table 11. FX2LP Pin Descriptions

128

TQFP

100

TQFP

56

SSOP

56

QFN

56 VF-

BGA

Name

Type

Default

Description

10

9

10

3

2D

AVCC

Power

N/A

Analog VCC. Connect this pin to 3.3V power source.

This signal provides power to the analog section of the

chip.

17

16

14

7

1D

AVCC

Power

N/A

Analog VCC. Connect this pin to 3.3V power source.

This signal provides power to the analog section of the

chip.

13

12

13

6

2F

AGND

Ground

N/A

Analog Ground. Connect to ground with as short a path

as possible.

20

19

17

10

1F

AGND

Ground

N/A

Analog Ground. Connect to ground with as short a path

as possible.

19

18

16

9

1E

DMINUS

IO/Z

Z

USB D– Signal. Connect to the USB D– signal.

18

17

15

8

2E

DPLUS

IO/Z

Z

USB D+ Signal. Connect to the USB D+ signal.

94

A0

Output

L

8051 Address Bus. This bus is driven at all times.

When the 8051 is addressing internal RAM it reflects

the internal address.

95

A1

Output

L

96

A2

Output

L

97

A3

Output

L

117

A4

Output

L

118

A5

Output

L

119

A6

Output

L

120

A7

Output

L

126

A8

Output

L

127

A9

Output

L

128

A10

Output

L

21

A11

Output

L

22

A12

Output

L

23

A13

Output

L

24

A14

Output

L

25

A15

Output

L

59

D0

IO/Z

Z

8051 Data Bus. This bidirectional bus is high

impedance when inactive, input for bus reads, and

output for bus writes. The data bus is used for external

8051 program and data memory. The data bus is active

only for external bus accesses, and is driven LOW in

suspend.

60

D1

IO/Z

Z

61

D2

IO/Z

Z

62

D3

IO/Z

Z

63

D4

IO/Z

Z

86

D5

IO/Z

Z

87

D6

IO/Z

Z

88

D7

IO/Z

Z

39

PSEN#

Output

H

Program Store Enable. This active-LOW signal

indicates an 8051 code fetch from external memory. It

is active for program memory fetches from

0x4000–0xFFFF when the EA pin is LOW, or from

0x0000–0xFFFF when the EA pin is HIGH.

Note

10. Unused inputs must not be left floating. Tie either HIGH or LOW as appropriate. Outputs should only be pulled up or down to ensure signals at power up and in

standby. Note also that no pins should be driven while the device is powered down.