Cypress Perform CY7C68013 User Manual

Page 25

CY7C68013A, CY7C68014A

CY7C68015A, CY7C68016A

Document #: 38-08032 Rev. *L

Page 25 of 62

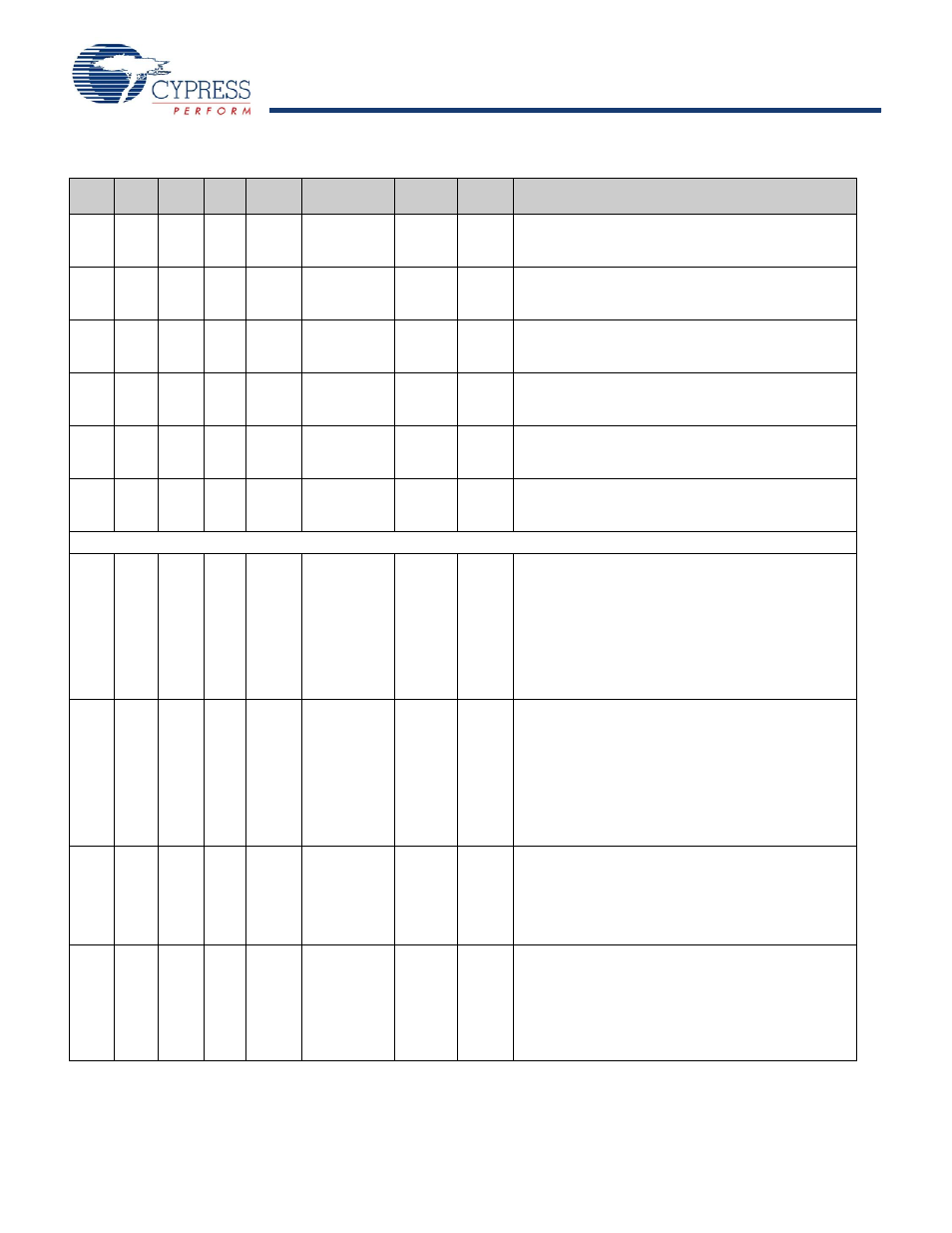

104

82

54

47

6B

PD2 or

FD[10]

IO/Z

I

(PD2)

Multiplexed pin whose function is selected by the

IFCONFIG[1..0] and EPxFIFOCFG.0 (wordwide) bits.

FD[10] is the bidirectional FIFO/GPIF data bus.

105

83

55

48

6A

PD3 or

FD[11]

IO/Z

I

(PD3)

Multiplexed pin whose function is selected by the

IFCONFIG[1..0] and EPxFIFOCFG.0 (wordwide) bits.

FD[11] is the bidirectional FIFO/GPIF data bus.

121

95

56

49

3B

PD4 or

FD[12]

IO/Z

I

(PD4)

Multiplexed pin whose function is selected by the

IFCONFIG[1..0] and EPxFIFOCFG.0 (wordwide) bits.

FD[12] is the bidirectional FIFO/GPIF data bus.

122

96

1

50

3A

PD5 or

FD[13]

IO/Z

I

(PD5)

Multiplexed pin whose function is selected by the

IFCONFIG[1..0] and EPxFIFOCFG.0 (wordwide) bits.

FD[13] is the bidirectional FIFO/GPIF data bus.

123

97

2

51

3C

PD6 or

FD[14]

IO/Z

I

(PD6)

Multiplexed pin whose function is selected by the

IFCONFIG[1..0] and EPxFIFOCFG.0 (wordwide) bits.

FD[14] is the bidirectional FIFO/GPIF data bus.

124

98

3

52

2A

PD7 or

FD[15]

IO/Z

I

(PD7)

Multiplexed pin whose function is selected by the

IFCONFIG[1..0] and EPxFIFOCFG.0 (wordwide) bits.

FD[15] is the bidirectional FIFO/GPIF data bus.

Port E

108

86

PE0 or

T0OUT

IO/Z

I

(PE0)

Multiplexed pin whose function is selected by the

PORTECFG.0 bit.

PE0 is a bidirectional IO port pin.

T0OUT is an active-HIGH signal from 8051

Timer-counter0. T0OUT outputs a high level for one

CLKOUT clock cycle when Timer0 overflows. If Timer0

is operated in Mode 3 (two separate timer/counters),

T0OUT is active when the low byte timer/counter

overflows.

109

87

PE1 or

T1OUT

IO/Z

I

(PE1)

Multiplexed pin whose function is selected by the

PORTECFG.1 bit.

PE1 is a bidirectional IO port pin.

T1OUT is an active-HIGH signal from 8051

Timer-counter1. T1OUT outputs a high level for one

CLKOUT clock cycle when Timer1 overflows. If Timer1

is operated in Mode 3 (two separate timer/counters),

T1OUT is active when the low byte timer/counter

overflows.

110

88

PE2 or

T2OUT

IO/Z

I

(PE2)

Multiplexed pin whose function is selected by the

PORTECFG.2 bit.

PE2 is a bidirectional IO port pin.

T2OUT is the active-HIGH output signal from 8051

Timer2. T2OUT is active (HIGH) for one clock cycle

when Timer/Counter 2 overflows.

111

89

PE3 or

RXD0OUT

IO/Z

I

(PE3)

Multiplexed pin whose function is selected by the

PORTECFG.3 bit.

PE3 is a bidirectional IO port pin.

RXD0OUT is an active-HIGH signal from 8051 UART0.

If RXD0OUT is selected and UART0 is in Mode 0, this

pin provides the output data for UART0 only when it is

in sync mode. Otherwise it is a 1.

Table 11. FX2LP Pin Descriptions (continued)

128

TQFP

100

TQFP

56

SSOP

56

QFN

56 VF-

BGA

Name

Type

Default

Description