Cypress Perform CY7C68013 User Manual

Page 22

CY7C68013A, CY7C68014A

CY7C68015A, CY7C68016A

Document #: 38-08032 Rev. *L

Page 22 of 62

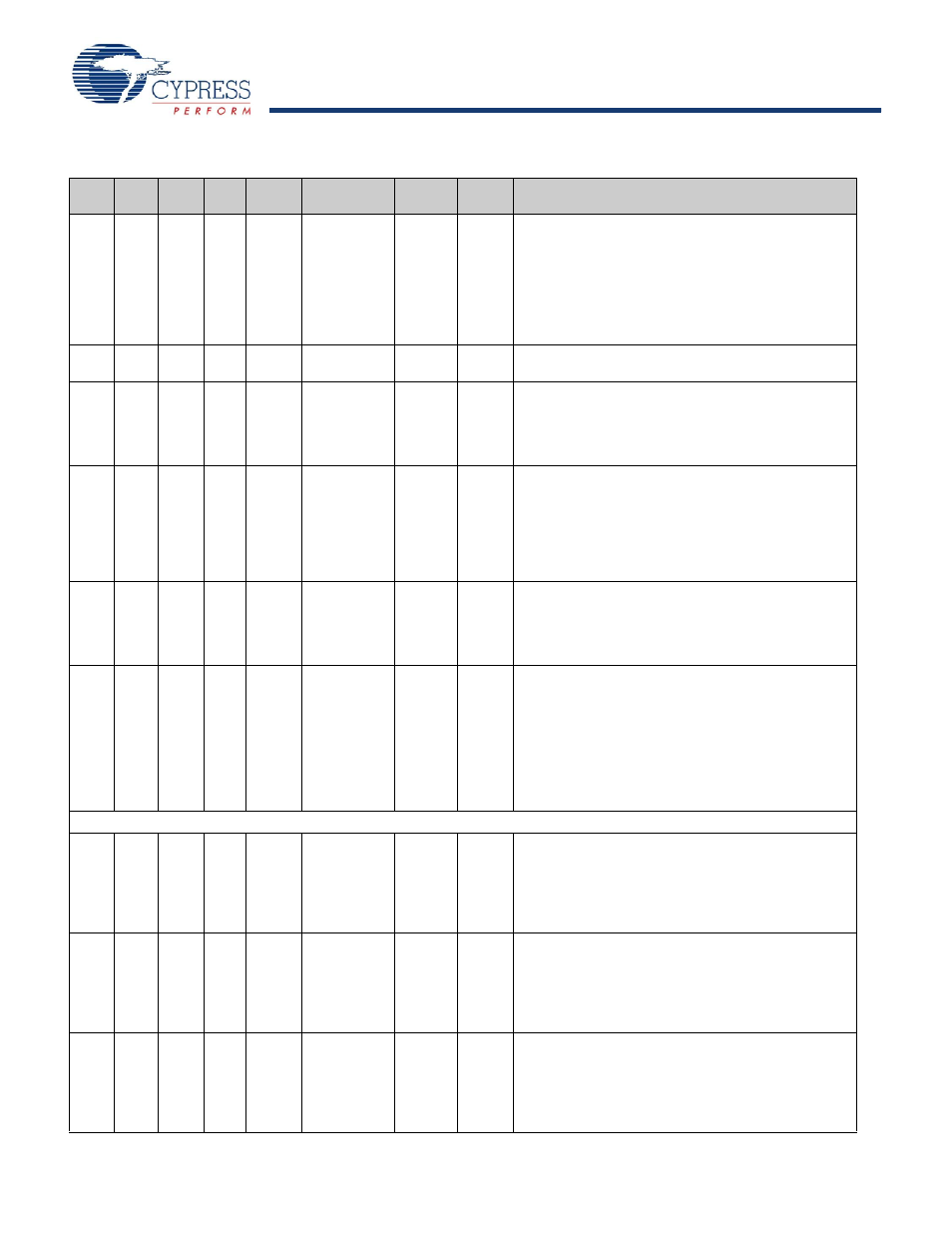

34

28

BKPT

Output

L

Breakpoint. This pin goes active (HIGH) when the 8051

address bus matches the BPADDRH/L registers and

breakpoints are enabled in the BREAKPT register

(BPEN = 1). If the BPPULSE bit in the BREAKPT

register is HIGH, this signal pulses HIGH for eight

12-/24-/48-MHz clocks. If the BPPULSE bit is LOW, the

signal remains HIGH until the 8051 clears the BREAK

bit (by writing 1 to it) in the BREAKPT register.

99

77

49

42

8B

RESET#

Input

N/A

Active LOW Reset. Resets the entire chip. See section

3.9 ”Reset and Wakeup” on page 6 for more details.

35

EA

Input

N/A

External Access. This pin determines where the 8051

fetches code between addresses 0x0000 and 0x3FFF.

If EA = 0 the 8051 fetches this code from its internal

RAM. IF EA = 1 the 8051 fetches this code from external

memory.

12

11

12

5

1C

XTALIN

Input

N/A

Crystal Input. Connect this signal to a 24-MHz

parallel-resonant, fundamental mode crystal and load

capacitor to GND.

It is also correct to drive XTALIN with an external

24-MHz square wave derived from another clock

source. When driving from an external source, the

driving signal should be a 3.3V square wave.

11

10

11

4

2C

XTALOUT

Output

N/A

Crystal Output. Connect this signal to a 24-MHz

parallel-resonant, fundamental mode crystal and load

capacitor to GND.

If an external clock is used to drive XTALIN, leave this

pin open.

1

100

5

54

2B

CLKOUT on

CY7C68013A

and

CY7C68014A

------------------

PE1 on

CY7C68015A

and

CY7C68016A

O/Z

-----------

IO/Z

12 MHz

----------

I

CLKOUT: 12-, 24- or 48-MHz clock, phase locked to the

24-MHz input clock. The 8051 defaults to 12-MHz

operation. The 8051 may three-state this output by

setting CPUCS.1 = 1.

------------------------------------------------------------------------

PE1 is a bidirectional IO port pin.

Port A

82

67

40

33

8G

PA0 or

INT0#

IO/Z

I

(PA0)

Multiplexed pin whose function is selected by

PORTACFG.0

PA0 is a bidirectional IO port pin.

INT0# is the active-LOW 8051 INT0 interrupt input

signal, which is either edge triggered (IT0 = 1) or level

triggered (IT0 = 0).

83

68

41

34

6G

PA1 or

INT1#

IO/Z

I

(PA1)

Multiplexed pin whose function is selected by:

PORTACFG.1

PA1 is a bidirectional IO port pin.

INT1# is the active-LOW 8051 INT1 interrupt input

signal, which is either edge triggered (IT1 = 1) or level

triggered (IT1 = 0).

84

69

42

35

8F

PA2 or

SLOE or

IO/Z

I

(PA2)

Multiplexed pin whose function is selected by two bits:

IFCONFIG[1:0].

PA2 is a bidirectional IO port pin.

SLOE is an input-only output enable with program-

mable polarity (FIFOPINPOLAR.4) for the slave FIFOs

connected to FD[7..0] or FD[15..0].

Table 11. FX2LP Pin Descriptions (continued)

128

TQFP

100

TQFP

56

SSOP

56

QFN

56 VF-

BGA

Name

Type

Default

Description